Fachhochschule Koblenz Fachbereich Ingenieurwesen Teilfachbereich Informationstechnik Konrad–Zuse–Straße 1 56075 Koblenz

# Diplomarbeit

# Entwurf und Aufbau eines neuartigen Kontinuum-Backends für die Radioastronomie mit digitaler Signalnachbearbeitung in Echtzeit

## von Vitaly Chetik

Abgabetag: 15.10.2007 Durchgeführt am:

Verfasser: Vitaly Chetik Max-Planck-Institut für Radioastronomie

Betreuender Professor: Prof. Dr. Berthold Gick Auf dem Hügel 69

Betreuer im Institut: Dr. Bernd Klein 53121 Bonn

Dr. Reinhard Keller

An dieser Stelle möchte ich allen danken, die zum Gelingen dieser Diplomarbeit beigetragen und mich tatkräftig unterstützt haben. Hierbei möchte ich folgende Personen hervorheben:

- meine Ehefrau Veronika Chetik, für die moralische Unterstützung und die Versorgung mit Kaffee besonders in den kurzen Nächten vor der Fertigstellung

- meine Eltern Vladimir und Vera Chetik, ohne deren Unterstützung mein Studium und schließlich diese Diplomarbeit nicht möglich gewesen wäre

- Herrn Prof. Dr.-Ing. Berthold Gick für seine Betreuung seitens der Fachhochschule

- Herrn Dr.-Ing. Reinhard Keller, Herrn Dr. rer. nat. Bernd Klein, Herrn Dipl.-Ing. Ingo Krämer und Herrn Dipl.-Ing. Andreas Bell für ihre starke Unterstützung und Betreuung, die sie mir in der vergangenen Zeit zukommen ließen

- Herrn Dipl.-Ing. Björn Hammen für die Unterstützung beim Gehäuseentwurf

- allen Mitarbeitern des Max-Planck-Institutes und besonders des Hochfrequenz-, Mikrowellen-, und Digitallabors, die mich jederzeit bei kniffligen Fragen unterstützten

(Vitaly Chetik)

# Inhaltsverzeichnis

| Aus | swahl c | ler Schnittstelle zum Kontrollraum       |

|-----|---------|------------------------------------------|

| _   | dware   |                                          |

| 3.1 |         | gschaltung                               |

|     | 3.1.1   | AD-Wandler AD7674                        |

|     | 3.1.2   | Operationsverstärker AD8022              |

|     | 3.1.3   | Bandbreite und Frequenzgang              |

|     | 3.1.4   | Einschwingverhalten                      |

|     | 3.1.5   | Nichtlineare Verzerrungen                |

|     | 3.1.6   | Gleichtaktstörunterdrückung CMRR         |

|     | 3.1.7   | Versorgungsspannung                      |

|     | 3.1.8   | Crosstalk                                |

| 3.2 |         | enzgang des Anti-Aliasing-Filters        |

| 3.3 |         | ngswiderstand                            |

| 3.4 |         | ngswiderstand der Schaltung              |

| 3.5 |         |                                          |

| 3.6 |         | ilter - Tusonix 4209-053                 |

|     | 3.6.1   | Frequenzgang                             |

|     | 3.6.2   | Sprungantwort                            |

|     | 3.6.3   | Gleichtaktstörung                        |

|     | 3.6.4   | Zusammenfassung                          |

| 3.7 |         | lschaltung                               |

|     | 3.7.1   | FPGA-Modul                               |

|     | 3.7.2   | Ethernet                                 |

|     | 3.7.3   | Digitale Steuersignale                   |

|     | 3.7.4   | RS-232 Schnittstelle                     |

|     | 3.7.5   | Bedienelemente                           |

|     | 3.7.6   | I <sup>2</sup> C-EEPROM - Atmel AT24C512 |

|     | 3.7.7   | Schnittstelle zum AD-Wandler AD7674      |

|     | 3.7.8   | IRIG-B AM-Demodulator                    |

#### Inhaltsverzeichnis

|   | 4.2<br>4.3<br>4.4 |                                                   | 44<br>45<br>45 |

|---|-------------------|---------------------------------------------------|----------------|

| 5 | Geh               | näuseentwurf                                      | 48             |

|   | 5.1               |                                                   | 48             |

|   | 0.1               | 8                                                 | 49             |

|   |                   | 5.1.2 Absorptionsverluste                         | 49             |

|   | 5.2               | Abschirmwirkung                                   | 50             |

|   | 0.2               | 5.2.1 Abschirmung von Magnetfeldern im NF-Bereich | 51             |

|   |                   | 5.2.2 Gehäuseöffnungen                            | 52             |

|   |                   | 5.2.3 Gehäuseresonanz                             | 52             |

|   | 5.3               |                                                   | 53             |

| 6 | Pro               | grammierung                                       | 56             |

| _ | 6.1               | Erweiterung des Ethernet-Moduls                   |                |

|   | 6.2               | <u>-</u>                                          | 57             |

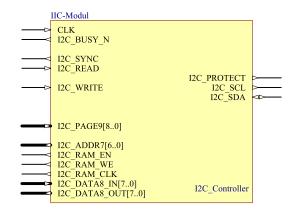

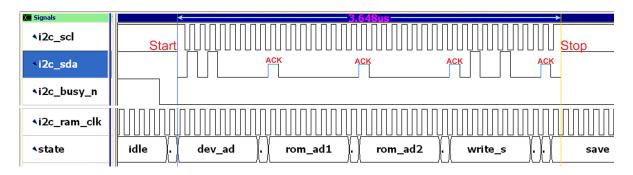

|   | 6.3               | Kommunikation mit dem I <sup>2</sup> C-EEPROM     | 58             |

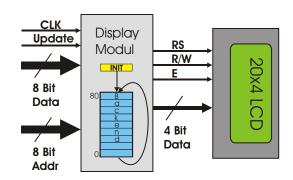

|   | 6.4               | Ansteuerung des Displays                          | 60             |

|   | 6.5               |                                                   | 61             |

|   | 6.6               |                                                   | 62             |

| 7 | Sigi              | nalverarbeitung                                   | 64             |

|   | 7.1               | •                                                 | 64             |

|   | 7.2               | Integralalgorithmus                               |                |

|   |                   | 7.2.1 Zusammenfassung                             | 67             |

| 8 | Stal              | oilität der Versorgungsspannung                   | 69             |

|   | 8.1               | Erwartungen                                       | 69             |

|   | 8.2               | Messgeräte und Aufbau                             | 70             |

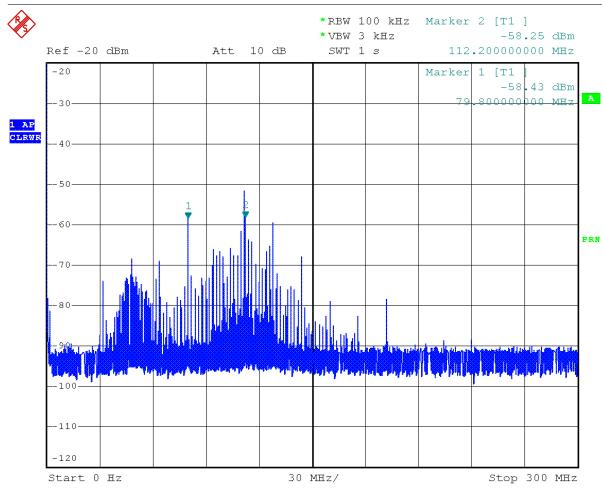

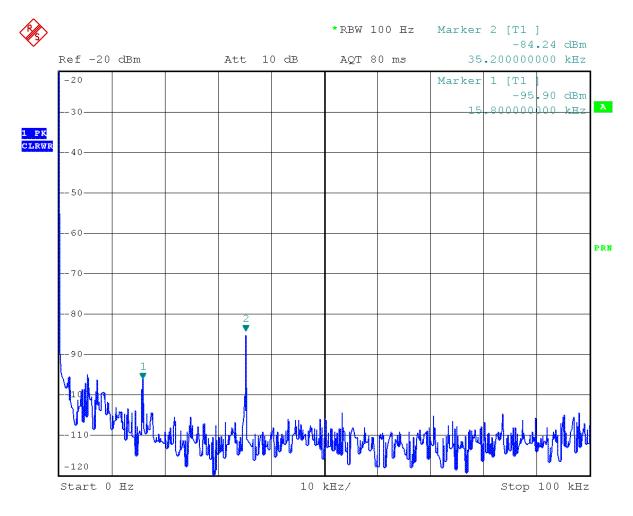

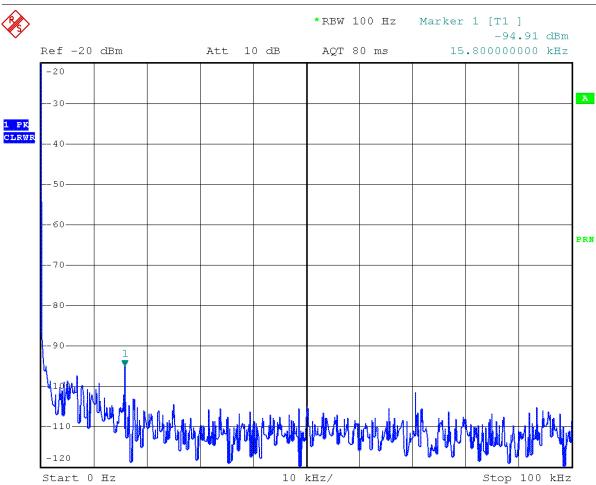

|   | 8.3               | Messergebnisse                                    | 71             |

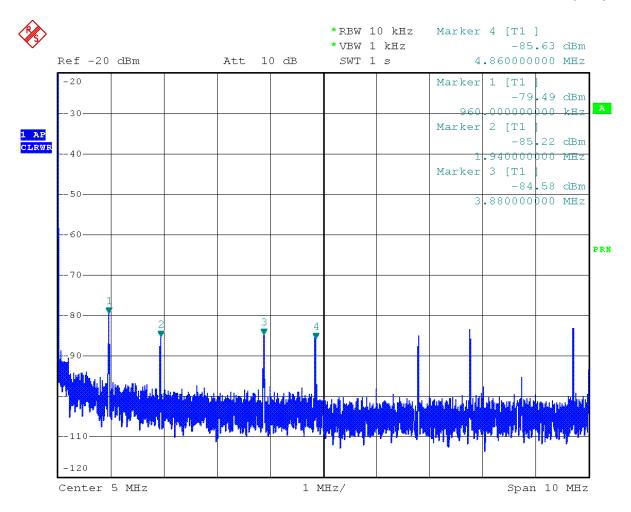

|   |                   | 8.3.1 Wirkung von Entstörgruppen                  | 71             |

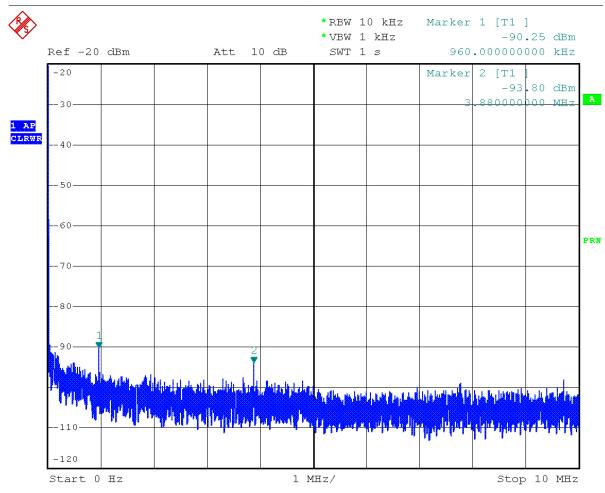

|   |                   | 8.3.2 Digitale Versorgungsspannung                | 73             |

|   |                   | 8.3.3 Analoge Versorgungsspannung                 | 74             |

|   |                   | 8.3.4 Analoge Eingänge                            | 77             |

|   | 8.4               | Zusammenfassung                                   | 78             |

| 9 | Unt               | ersuchung der Analogschaltung                     | 79             |

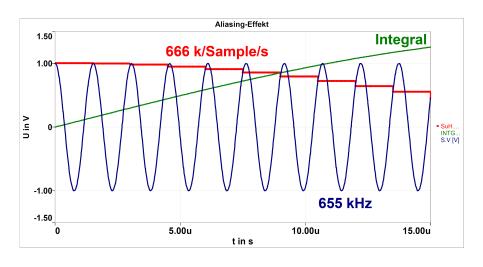

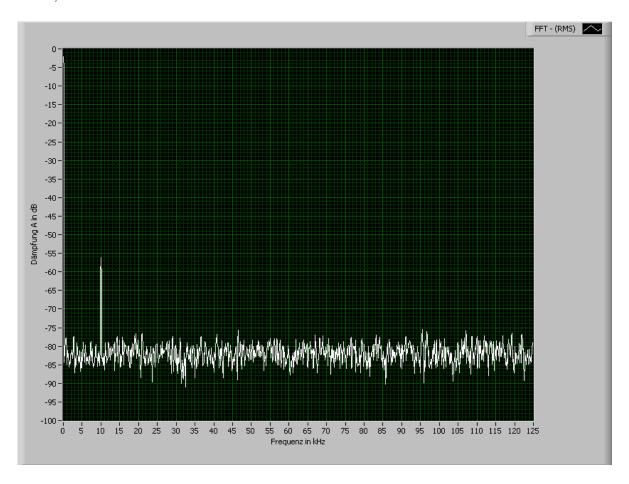

|   | 9.1               | Rauschen                                          | 80             |

|   | 9.2               | Aliasing-Effekte                                  | 81             |

|   | 9.3               | Gleichtaktstörunterdrückung (CMRR)                | 82             |

|   | 9.4               | Einschwingverhalten                               | 83             |

|   | 9.5               | Verzerrungen                                      | 84             |

|   | 9.6               | Übersprechen der benachbarten Kanäle              | 85             |

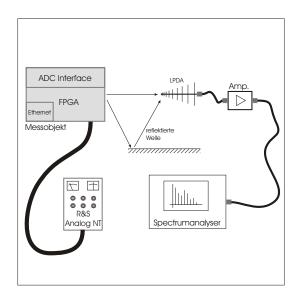

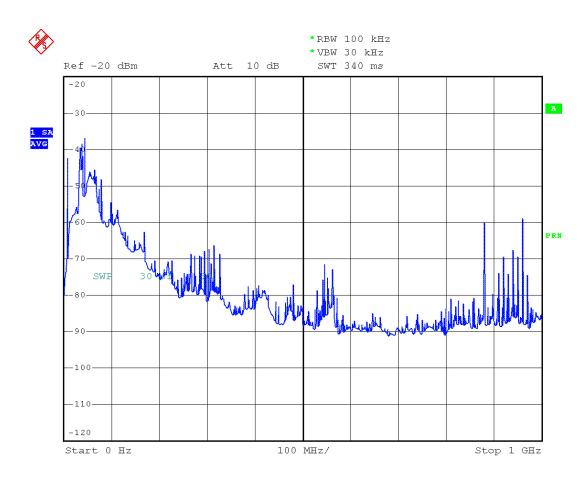

| 10 | EMV-Messung                         | 86  |

|----|-------------------------------------|-----|

|    | 10.1 Einführung                     | 86  |

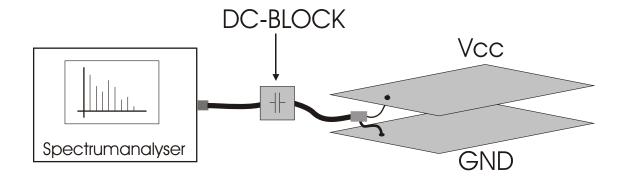

|    | 10.2 Messaufbau                     | 87  |

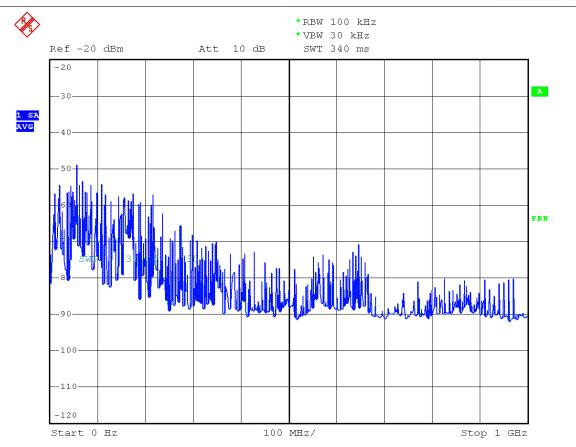

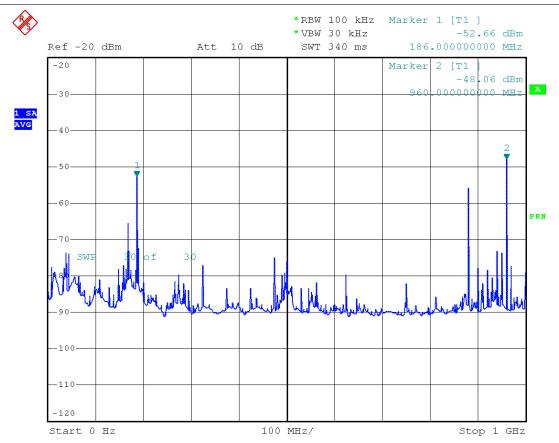

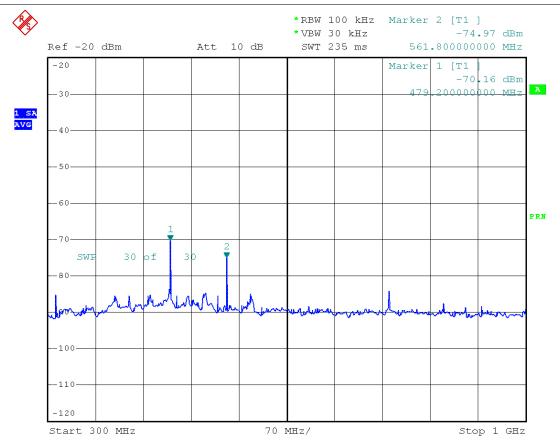

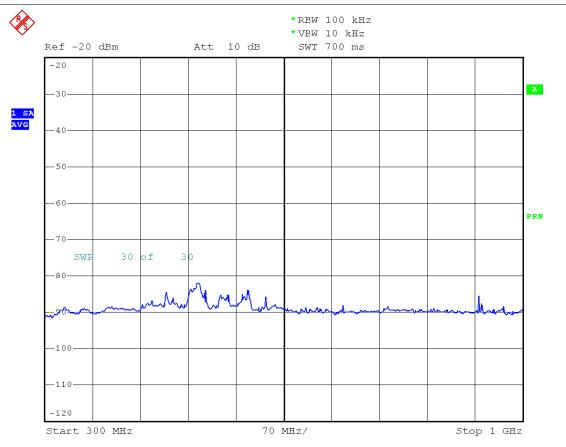

|    | 10.3 Nahfeldmessung                 | 87  |

|    | 10.3.1 Ergebnis der Nahfeldmessung  | 87  |

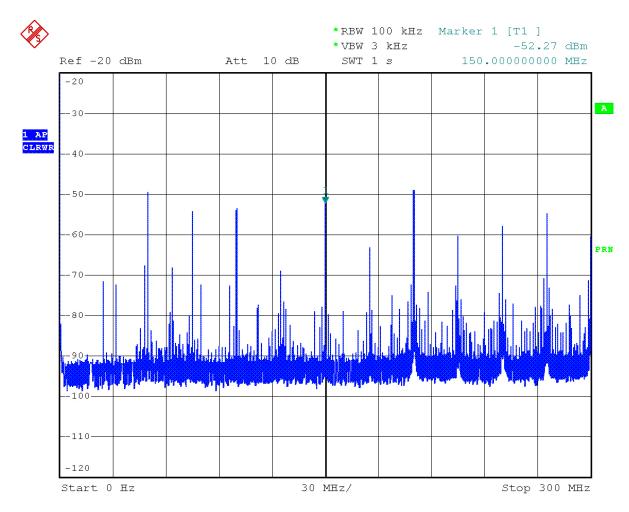

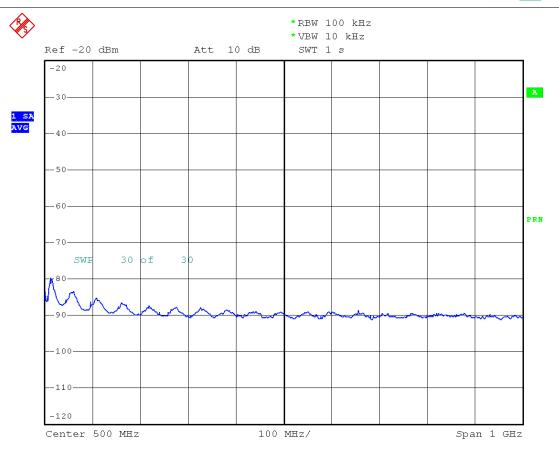

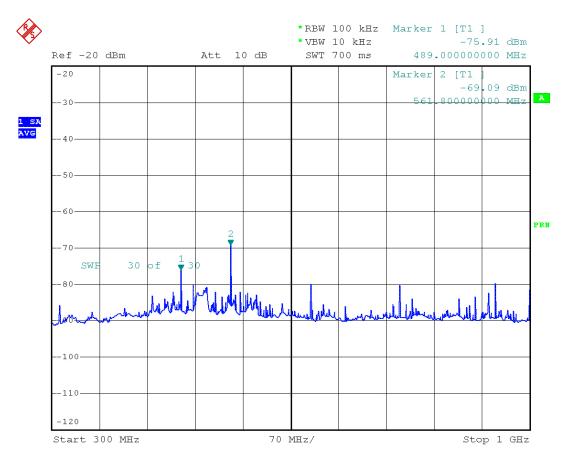

|    | 10.4 Fernfeldmessung                | 91  |

|    | 10.4.1 Ergebnis der Fernfeldmessung | 92  |

|    | 10.5 Zusammenfassung                | 94  |

| A  | Schaltpläne                         | 95  |

| В  | Datenblätter                        | 102 |

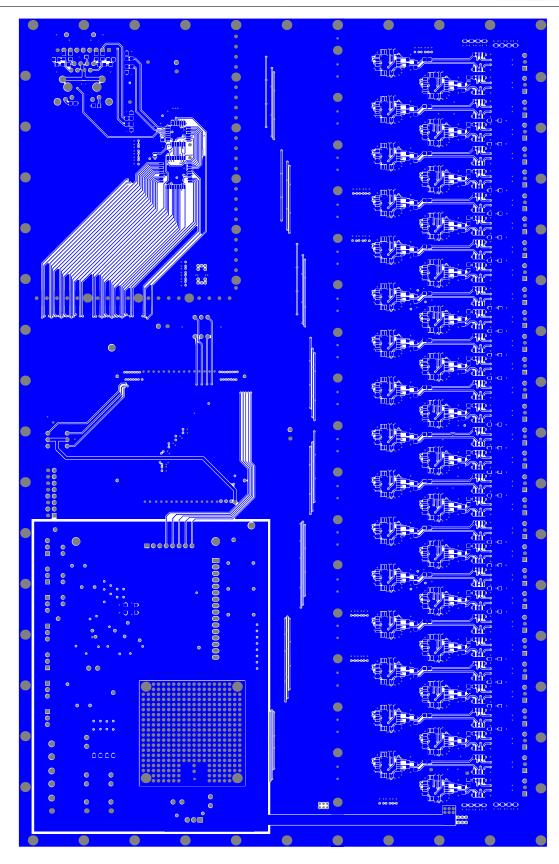

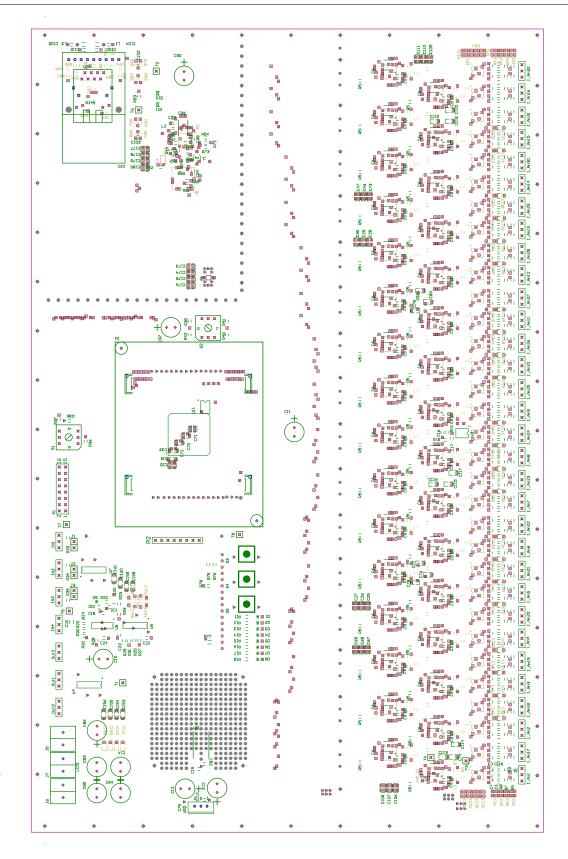

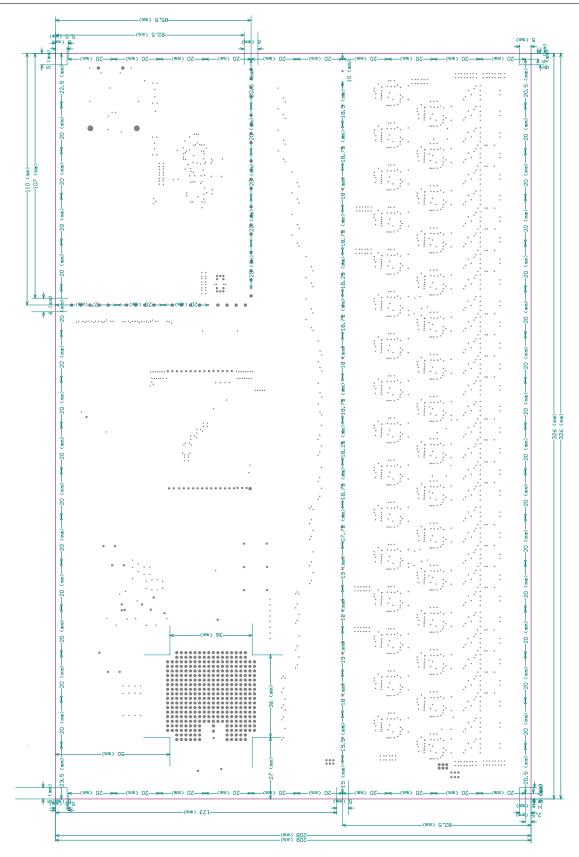

| С  | Layout                              | 103 |

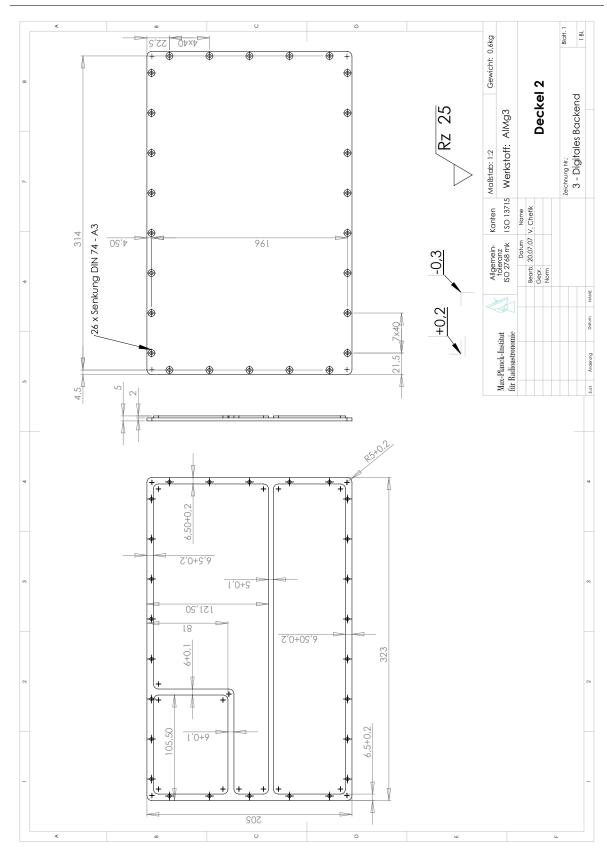

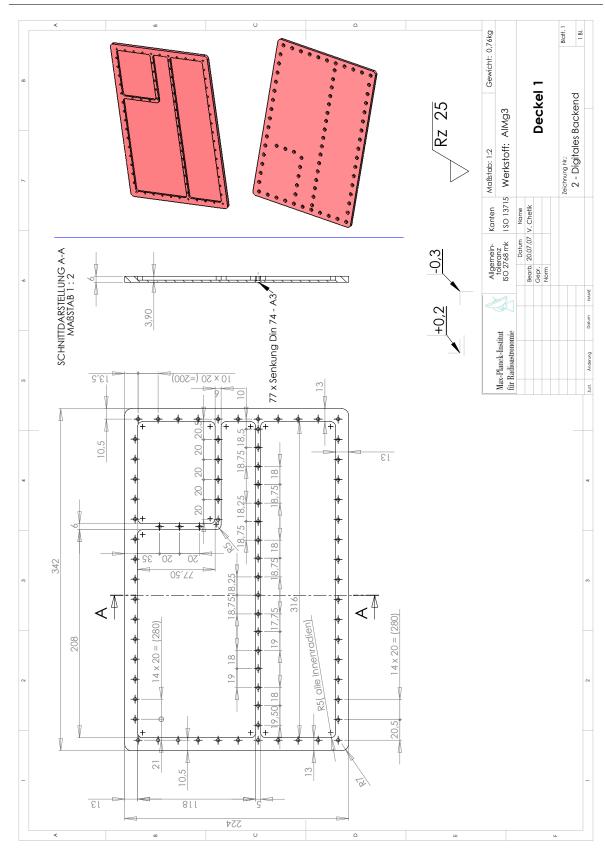

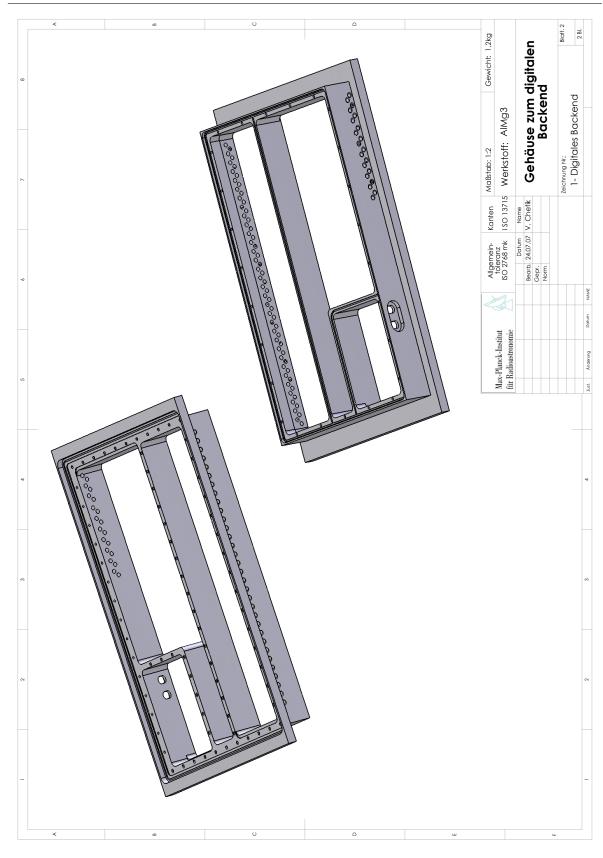

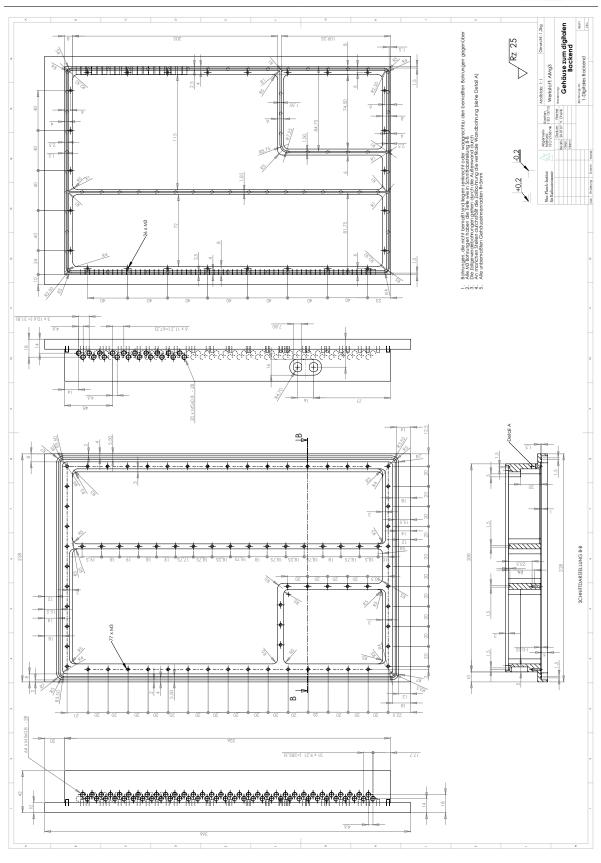

| D  | Gehäuse                             | 113 |

| Ε  | Programmierung                      | 119 |

| F  | Literaturverzeichnis                | 120 |

# Erklärung

lch versichere hiermit, dass ich diese Arbeit selbstständig und ohne Benutzung anderer als der angegebenen Quellen angefertigt habe. Diese Arbeit wurde in gleicher oder ähnlicher Form noch keiner anderen Prüfungsbehörde vorgelegt und auch nicht veröffentlicht.

| Bonn, | am | 15. | Oktobei  | r 2007 |  |

|-------|----|-----|----------|--------|--|

|       |    |     |          |        |  |

|       |    | Vit | aly Chet | ik     |  |

# 1 Einführung

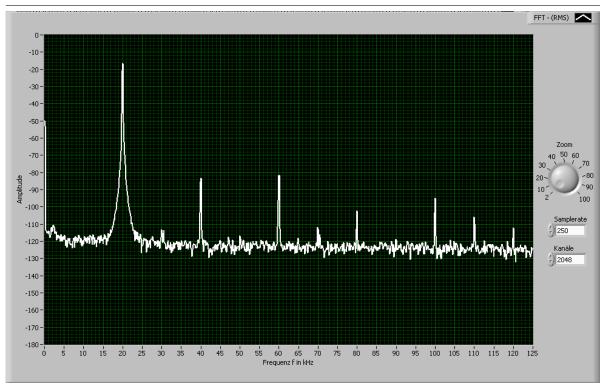

Für die Erfassung und Verarbeitung der Empfangssignale sitzt am Ende der Empfangskette das sogenannte »Backend«. In der Radioastronomie gibt es eine Vielzahl an Backend-Typen, die je nach Empfangs- und Beobachtungsart unterschiedliche Aufgaben zu erfüllen haben. Es gibt z.B. das FFT-Spektrometer, das eine Spektralanalyse der Empfangsdaten ermöglicht, oder das hier entwickelte Kontinuum-Backend, das eine Erfassung der »Total Power« am Detektor ermöglicht.

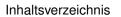

Das bis jetzt eingesetzte Empfangssystem der Kontinuumempfänger funktioniert nach dem Prinzip in Abbildung 1.1. Das empfangene Signal durchläuft eine Reihe von Verstärkern und Mischern und wird am Detektor als Signalleistung interpretiert und in eine proportionale Gleichspannung umgesetzt. Der Detektor besteht im einfachsten Falle aus einer Diode mit einer quadratischen Kennlinie, die das Eingangssignal gleichrichtet oder mathematisch ausgedrückt mit der Gleichung 1.1,

$$A \cdot \sin^2(x) = \frac{A}{2} + \frac{A}{2} \cdot \sin(2 \cdot x) \tag{1.1}$$

eine Frequenzumsetzung verursacht. Um die am Detektor gewonnene Gleichspannung ohne Verluste und Fehlereinflüsse an das Backend übertragen zu können, wird die Gleichspannung durch einen Spannungs-Frequenz-Umsetzer (V/F-Converter), wie der Name schon sagt, in Frequenz (Taktsignal) umgesetzt. Um eine Übertragungsstrecke von ca. 350 m überwinden zu können, werden RS-422 Leitungstreiber verwendet. Das am Backend ankommende Taktsignal inkrementiert einen Zähler über eine festgelegte Messdauer und ermöglicht durch Auswertung des Zählerstandes die Bestimmung der Leistung am Detektor.

Abbildung 1.1: Bestehendes System in Effelsberg

mit V/F-Converter

Das Max-Planck-Institut für Radioastronomie entwickelt derzeit einen neuen 7-beam 32 GHz Empfänger für das 100-m-Radioteleskop in Effelsberg. Die in diesem Kontinuumempfänger eingesetzten cryogenen¹ Verstärker basieren auf MMICs² in InP³-Technologie, die gegenüber den bei niedrigeren Frequenzen verwendeten HEMTs⁴ in GaAs-Technologie eine stärkere 1/f Gain-Instabilität aufweisen. Zur Kompensation dieser inhärenten Schwankungen wird der Empfänger als geschalteter Pseudo-Korrelations-Empfänger aufgebaut. Hierzu werden in allen Frontend-Kanälen elektronische 180°-Phasenschalter in MMIC-Technik eingesetzt, die durch zyklisches Schalten jeweils die beiden Kanäle eines korrelierten Signalzuges gegeneinander vertauschen. Theoretische Überlegungen sowie die Auslegung ähnlicher Empfänger zeigen, dass die benötigte Schaltfrequenz für eine Senkung der Gain-Fluktuation zum Gesamtrauschen von ungefähr 10 % im Bereich von einigen kHz liegt. Schaltfrequenzen im kHz-Bereich liegen außerhalb der technischen Möglichkeiten des vorhandenen Backends für Kontinuum-Beobachtungen, das auf den bereits genannten V/F-Convertern und binären Zählern basiert. Deshalb soll ein neues Backend entwickelt werden, welches den Ansprüchen des neuen Kontinuumempfängers gerecht wird.

## 1.1 Aufgabenstellung

Gegenstand der vorliegenden Diplomarbeit war der Entwurf und Aufbau eines neuen Kontinuum-Backends für die Radioastronomie mit digitaler Signalnachbearbeitung in Echtzeit. Dabei sollten die im Folgenden aufgeführten Anforderungen beachtet und verwirklicht werden:

- Entwicklung der notwendigen Hardware:

- mindestens 24 analoge Eingänge mit 18 Bit AD-Wandlern für die Erfassung der zur Leistung proportionalen Gleichspannung am Detektor und anderer Signale

- digitale Ein- und Ausgänge mit RS-422 Schnittstellen für die Steuersignale (Blank, Sync, Chop)

- IRIG-B<sup>5</sup>-Demodulator für die zeitliche Dokumentation der Messdaten

<sup>&</sup>lt;sup>1</sup>Flüssiges Helium oder Stickstoff sorgt für eine Abkühlung des Verstärkers auf eine Temperatur von wenigen Kelvin.

<sup>&</sup>lt;sup>2</sup>monolithisch integrierter Mikrowellenschaltkreis

<sup>&</sup>lt;sup>3</sup>Indiumphosphid, Halbleiterverbindung die besonders gut für die Hochfrequenztechnik geeignet ist

<sup>&</sup>lt;sup>4</sup>High Electron Mobility Transistor

<sup>&</sup>lt;sup>5</sup>GPS basiertes Zeitsignal

- Verwendung eines passenden FPGAs<sup>6</sup> für die Abdeckung der gesamten Steuerung des Backends und zur Ermöglichung der digitalen Signalverarbeitung.

- Entwicklung einer geeigneten Schnittstelle für die Übertragung der Daten zum Kontrollraum, ohne die Empfänger und andere analoge Baugruppen zu stören.

- Entwicklung eines EMV-dichten Gehäuses, da das Backend sich in der Umgebung eines hoch empfindlichen, cryogenisch gekühlten Empfangssystems befindet.

# 1.2 Zusammenfassung der Ergebnisse

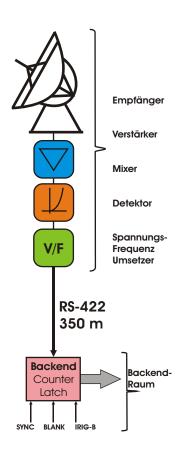

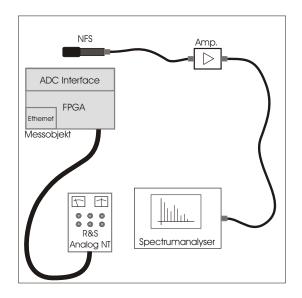

Bei der Durchführung der Diplomarbeit konnten alle der zuvor genannten Ansprüche realisiert und Probleme gelöst werden. Die Abbildung 1.2 zeigt den Aufbau des Empfangssystems mit dem neuen Backend.

Das in dieser Arbeit entwickelte Backend bietet:

- 32 analoge Eingangskanäle mit 18 Bit AD-Wandlern

- Es ermöglicht eine direkte Signalerfassung nach dem Detektor ohne zusätzliche V/F-Converter

- Variable Schaltfrequenz (CHOP-Signal) für die Vertauschung der Kanäle am Verstärker, somit lässt sich die optimale Schaltfrequenz ermitteln

- Ein EMV-dichtes Gehäuse für eine störungsfreie Funktion der Empfänger

- Eine optische 100Base-FX Schnittstelle, die eine optimale Übertragungsrate zum Kontrollraum ermöglicht, ohne die Umgebung zu stören

- Einen leistungsfähigen Xilinx-FPGA für die notwendige Signalnachbearbeitung

Lediglich das Erreichen der vollen 18 Bit Auflösung, bedingt durch die vorhandene nicht ausreichende Analogschal-

Abbildung 1.2: Das neue digitale Backend den für 7-beam 32 GHz Empfänger

tung, erwies sich als schwierig (Begründung dafür und anzustrebende Lösungswege werden an entsprechender Stelle erläutert).

<sup>&</sup>lt;sup>6</sup>Field Programmable Gate Array

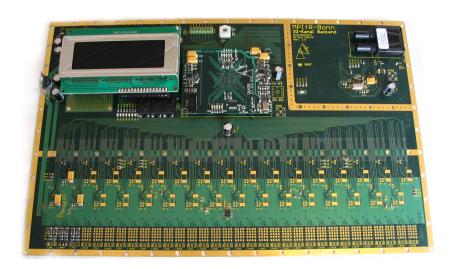

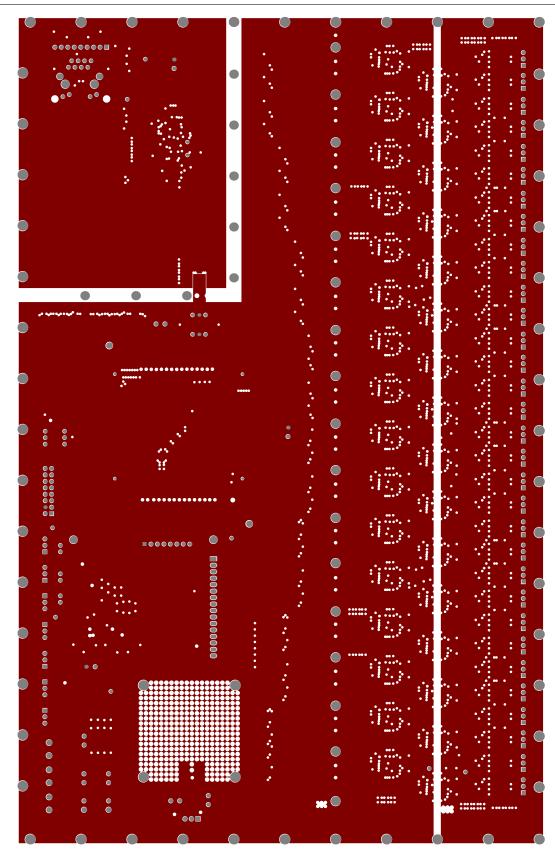

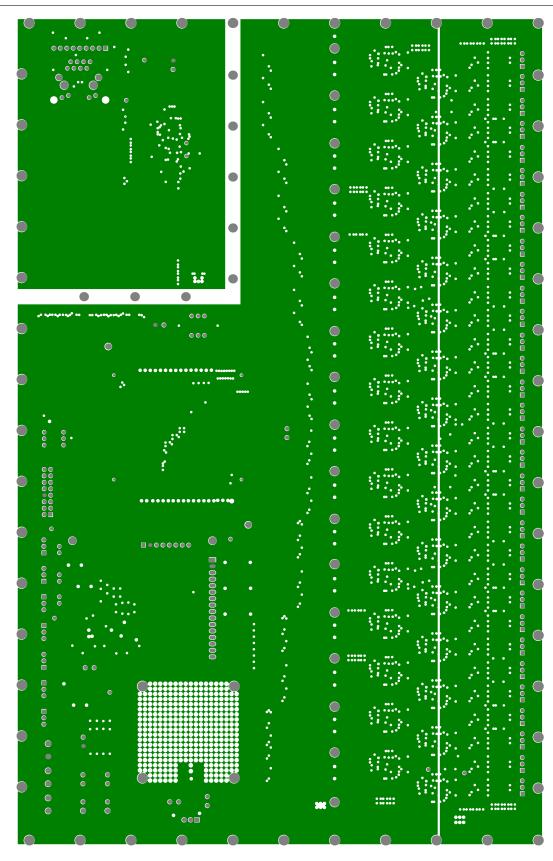

Die Abbildungen 1.3 und 1.4 zeigen den realisierten Prototyp und die Hardware des neuen Backends.

Abbildung 1.3: Das neue 32-Kanal-Backend

Abbildung 1.4: Realisierte Hardware

Die vorliegende Dokumentation gibt die Ergebnisse der Arbeit detailliert wieder und zeigt auf, wie die genannten Vorgaben verwirklicht wurden.

# 2 Auswahl der Schnittstelle zum Kontrollraum

Wie schon in der Einleitung erwähnt, befindet sich das neue Backend in unmittelbarer Nähe zum Empfänger und darf diesen auf keinen Fall stören. Die durch das Backend erzeugten elektromagnetischen Störungen können zwar durch ein EMV-gerechtes Layout und Gehäuse unterdrückt werden, ändern aber nichts an der Erzeugung elektromagnetischer Störungen in der Übertragungsstrecke zum Kontrollraum. Deshalb wurde nach einer Übertragungsmöglichkeit gesucht, die keine Auswirkungen auf den Empfänger und andere Baugruppen hat.

Um eine Auswahl an möglichen Schnittstellen aufzustellen, wurde zuerst die bestehende Installation in Effelsberg untersucht. Die Untersuchung ergab, dass eine Vielzahl an Twisted-Pair-Kabeln sowie einige Singelmode- und Multimode-Glasfasern zur Verfügung stehen. Zusätzlich werden einige Multimode-Glasfasern nachinstalliert. Die maximale Übertragungstrecke vom Teleskop zum Kontrollraum beträgt ca. 350 Meter und grenzt damit die Auswahl an verfügbaren Übertragungsmöglichkeiten stark ein.

Aufgrund der großer Entfernung zum Kontrollraum und der notwendigen hohen Datenrate kommen die meisten gängigen Schnittstellen nicht in Frage. In Tabelle 2.1 werden einige Schnittstellen zum Vergleich dargestellt. Auf eine Auflistung paralleler Schnittstellen wurde verzichtet, da diese aufgrund der Entfernung nicht in Frage kommen.

| Schnittstelle | Datenrate | Maximale      |  |  |  |

|---------------|-----------|---------------|--|--|--|

|               |           | Leitungslänge |  |  |  |

| RS232         | gering    | < 10m         |  |  |  |

| RS422         | gering    | < 500m        |  |  |  |

| 100Base-TX    | hoch      | < 100m        |  |  |  |

| 100Base-FX    | hoch      | < 400/2000m   |  |  |  |

Tabelle 2.1: Auflistung einiger Schnittstellen

Wie man der Tabelle 2.1 entnehmen kann, scheint die Ethernetschnittstelle eine optimale Lösung zu sein. Die weit verbreitete 100Base-TX Schnittstelle ist fast in jedem Computer zu finden und stellt damit eine passende Gegenstelle zur Verfügung. Eine Übertragungsstrecke von mehr als 100 Metern lässt sich durch Zwischenschalten von Repeatern realisieren. Das einzige Problem liegt in der Abstrahlung von elektromagnetischen Wellen durch das Kupferkabel. Um eine Gleichstromunterdrückung und Taktrückgewinnung zu ermöglichen, durchlaufen die Daten einen 4B5B-Codierer sowie einen Scrambler. Das Ergebnis ist eine gleichmäßige Verteilung der Leistung über die gesamte Bandbreite. Störungen dieser Art verringern den Signal-Rausch- und Signal-Störabstand in den analogen Gruppen und lassen sich nur sehr schwer aus den Messdaten entfernen. Auch wenn man ein mehrfach abgeschirmtes Twisted-Pair-Kabel, z.B. SF/FTP, verwenden würde, könnte die Abstrahlung nicht komplett unterdrückt werden.

Um die Datenübertragung ohne Störung des Empfängers zu ermöglichen, kommt nur eine optische Übertragungsstrecke in Frage. Die Vorteile einer optischen Übertragungsstrecke liegen nicht nur in der elektromagnetischen Verträglichkeit, sondern auch in der deutlich längeren Übertragungsstrecke ohne Repeater. Der 100Base-FX Standard definiert eine Datenübertragung über Glasfaser und ist eine gute Alternative zu 100Base-TX. Die maximale Segmentlänge der Übertragungsstrecke kann durch Verwendung von leistungsfähigen Transceivern erweitert werden. Die genaue Realisierung der beiden Schnittstellen wird in Abschnitt 3.7.2 auf Seite 30 näher beschrieben.

# 3 Hardware

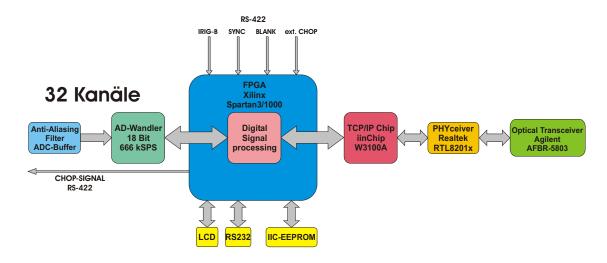

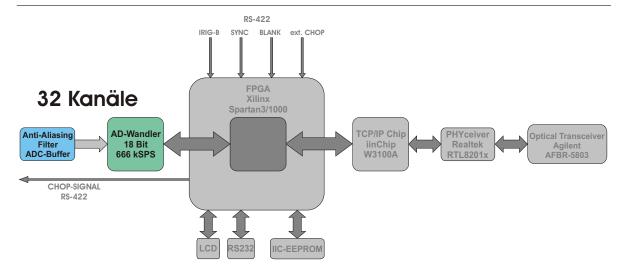

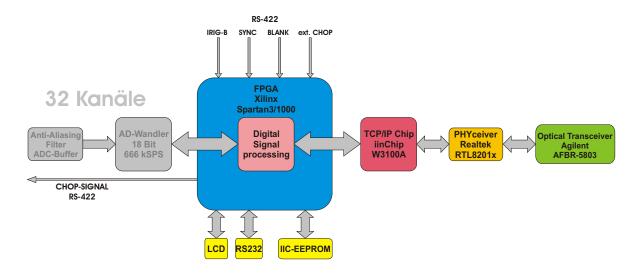

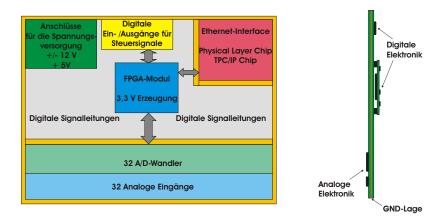

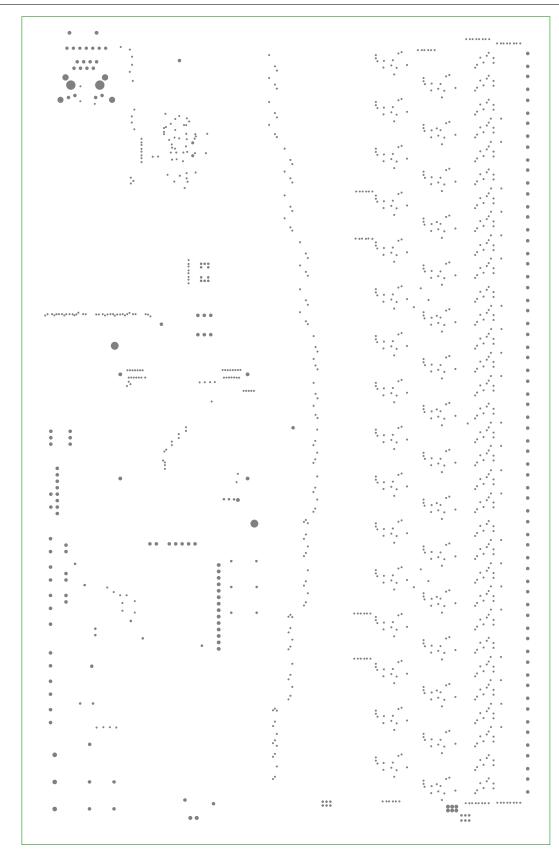

Das Blockschaltbild in Abbildung 3.1 zeigt die gesamte Hardware des neuen Backends. Die einzelnen Baugruppen werden in den nachfolgenden Abschnitten ausführlich erläutert.

Abbildung 3.1: Blockschaltbild zur gesamten Hardware

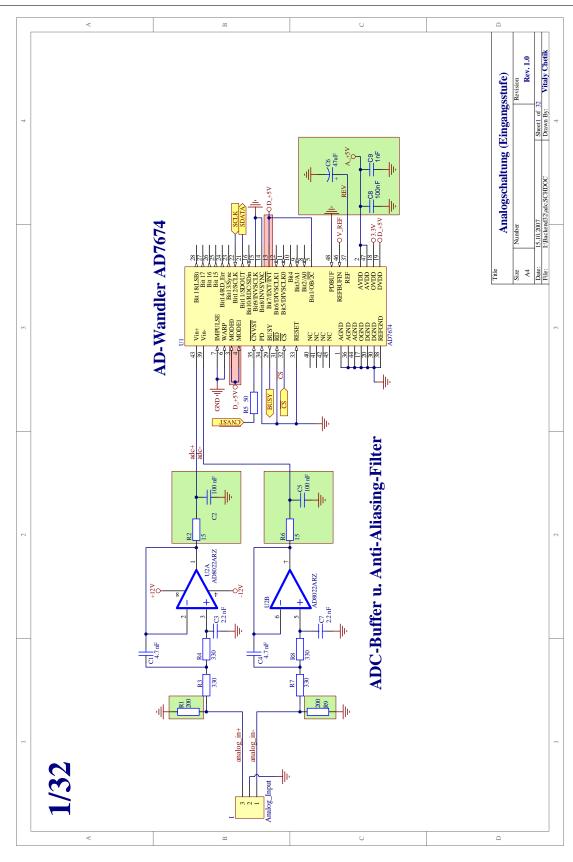

# 3.1 Analogschaltung

Bei der Analogschaltung handelt es sich um eine bereits in einer vorhergehenden Arbeit untersuchten Filter-Variante, die als Anti-Aliasing-Filter und ADC-Buffer für einen 18 Bit AD-Wandler dienen soll. Dabei wurden mehrere Typen mit Hilfe des Online-Tools » Analog Filter Wizard « von » Analog Devices « entworfen und auf den Frequenzgang untersucht. Das Konzept wurde an dieser Stelle aufgegriffen und für das neue Backend realisiert.

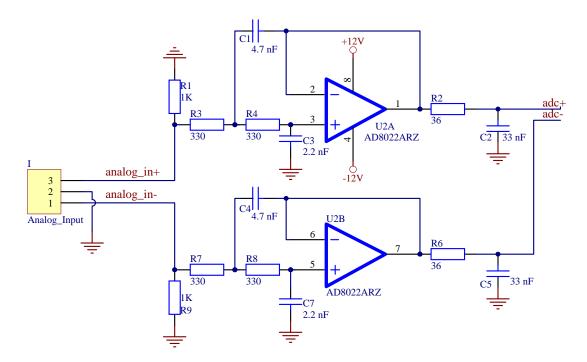

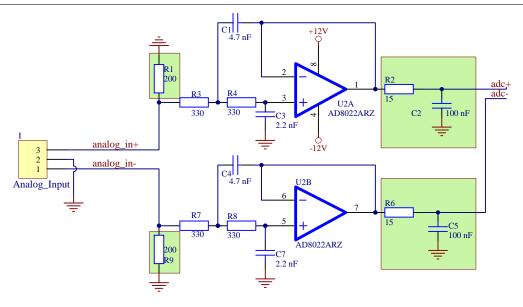

Die Abbildung 3.2 auf der nächsten Seite zeigt die realisierte Analogschaltung des neuen Backends (farblich hervorgehoben). Sie besteht aus 32 analogen Eingangskanälen mit 18 Bit AD-Wandlern.

Abbildung 3.2: Blockschaltbild zur analogen Hardware

In Abbildung 3.3 ist die analoge Eingangsstufe ohne den AD-Wandler dargestellt. Das Filter besteht aus einem Bessel-Tiefpass 2. Ordnung mit nachgeschaltetem RC-Glied. Die Vorteile eines Bessel-Tiefpasses liegen hauptsächlich in seinem geringen Überschwingverhalten und kurzer Einschwingdauer auf sprunghafte Anregung. Für die Realisierung eines differentiellen Ein- und Ausgangs wurde das Filter in doppelter Ausführung verwendet.

Abbildung 3.3: Analoge Eingangsstufe

Bei der vorangegangenen Festlegung der Schaltung hat man sich hauptsächlich auf die »Application Notes« des Herstellers verlassen und auf eine nähere Untersuchung verzichtet. Aus den bestehenden Messergebnissen ließ sich jedoch keine genaue Aussage über die Störunempfindlichkeit und tatsächliche Bitauflösung machen.

Deshalb wurde die vorgeschlagene Schaltung in Bezug auf den zu verwendenden 18 Bit AD-Wandler AD7674 nochmals untersucht. In den einzelnen Teilabschnitten wird eine theoretische Betrachtung und Realisierung der gesamten Analogschaltung durchgeführt und auf ihre Grenzen hingewiesen.

#### 3.1.1 AD-Wandler AD7674

Für die Digitalisierung der Messdaten soll ein möglichst hochauflösender und schneller AD-Wandler verwendet werden, damit man in den kurzen Messphasen von ca. 250/500  $\mu$ s einen möglichst hohen Informationsgehalt erreicht. An den zu verwendenden AD-Wandler wurden deshalb folgende Ansprüche gestellt:

- 100 kHz Bandbreite für Eingangssignale

setzt eine minimale Abtastrate > 200 kSample/s voraus

- 18 Bit Auflösung

- hoher Dynamikbereich

- geringe Wandlungszeit bei sprunghafter Anregung

- differentieller Eingang

- hoher Signal-Rauschabstand

Der zum Einsatz kommende AD7674 ist im Augenblick einer der leistungsfähigsten SAR (sukzessive Approximation) AD-Wandler auf dem Markt und erreicht bei einer maximalen Abtastrate von 800/666 kSample/s eine Auflösung von bis zu 18 Bit. Die Auflistung zeigt einige wichtige Eigenschaften des AD7674:

- 103 dB Dynamikbereich

- 18 Bit Auflösung

- 100 dB S/(N+D) @ (2 kHz)

- 666 kSample/S (Normal mode)

- serielle/parallele Datenübertragung

- No pipeline delay SAR architecture (sukzessive Approximation)

- differentieller Eingang

Der große Dynamikbereich des AD7674 ermöglicht Messungen von  $\pm 31,25~\mu V$  (1LSB) bis  $\pm 4,096~V$  (Full Scale Range) ohne zusätzliche Verstärkung. Die hohe Abtastrate mit 666 kSample/s liegt weit über der gewünschten Abtastrate und ermöglicht bei einer Messdauer von 250  $\mu s$  ca. 166 Stichproben. Um die Maximalwerte des AD-Wandlers zu erreichen, müssen sehr hohe Ansprüche an die Versorgungsspannung und restliche Schaltung gestellt werden. Die meisten nicht idealen Eigenschaften des AD7674 können zwar nicht direkt verbessert oder beeinflusst werden, es ist aber gut ihre Grenzen zu kennen und bei der Auslegung der Anti-Aliasing-Filter und ADC-Treiber (ADC-Buffer) zu berücksichtigen. Die Angaben der Hersteller werden nur unter idealen Bedingungen erreicht und können in der Praxis nur näherungsweise realisiert werden. Die nachfolgenden Untersuchungen erläutern einige wichtige Parameter, die eine direkte Auswirkung auf die Eigenschaften des AD-Wandlers haben und bei der Realisierung der Schaltung berücksichtigt wurden.

#### 3.1.1.1 Temperaturabhängigkeit

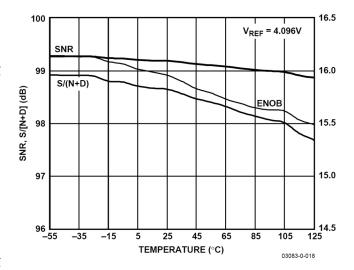

Mit steigender Temperatur verschlechtert sich zum einen der Signal-Rauschabstand (S/N) und zum anderen steigt die harmonische Verzerrung an. Die Abbildung 3.4 zeigt den direkten Einfluss der Temperatur auf den Signal-Rauschabstand inkl. Verzerrung und die effektive Anzahl an Bits (ENOB). Besonders auffällig ist die Steigung der Verzerrung, wobei der S/N nur langsam abfällt. Aus der Summe der beiden (S/[N+D]) lässt sich nach Gleichung 3.1 die ENOB berechnen.

Figure 18. SNR, S/(N+D), and ENOB vs. Temperature

$$ENOB = \frac{\frac{S}{N+D} - 1.76}{6.02} \tag{3.1}$$

Abbildung 3.4: Temperatureinfluss auf die effektive Anzahl an Bits (Analog Devices)

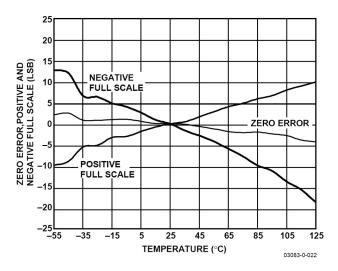

Die Abbildung 3.5 zeigt die Abhängigkeit des Verstärkungsfehlers (Gain Error) und des Offset-Fehlers (Zero Error) von der Temperatur. Auch wenn der Gain Error ein systematischer Fehler ist, so lässt er sich nicht wie der Zero Error durch Differenzmessungen kompensieren. Für eine maximale Genauigkeit wird deshalb eine Umgebungstemperatur von ca. 25° C gefordert.

Figure 22. Zero Error, Positive and Negative Full Scale vs. Temperature

Abbildung 3.5: Gain Error und Zero Error durch Temperatureinfluss (Analog Devices)

#### 3.1.1.2 Versorgungsspannung

Der AD7674 hat insgesamt drei Versorgungsspannungen. Zwei davon werden für den digitalen Bereich verwendet und eine für den analogen. Die Auflistung zeigt die notwendigen Spannungen:

- +5V analog

- +5V digital (interne Logik)

- +3,3V/+5V digital (I/O-Interface)

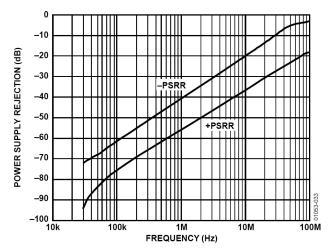

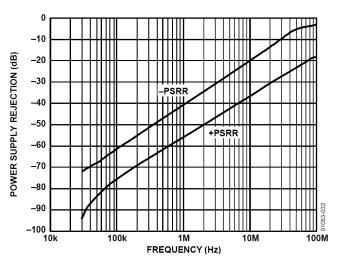

Für maximale Auflösung und hohen Signal-Rauschabstand sollte die analoge Versorgungsspannung nicht mit der digitalen verbunden werden. Auch wenn der AD7674 eine durchaus hohe Netzstörunterdrückung (PSRR) von 60 dB

Power Supply Rejection vs. Frequency  $V_S = \pm 12 V$

Abbildung 3.6: Netzstörunterdrückung PSRR (Analog Devices)

hat, so wird diese aber nur bis 100 kHz erreicht (Abbildung 3.6). Danach ist ein starker Abfall zu beobachten. Störungen ab 100 MHz können nahezu ungedämpft auf den AD-Wandler

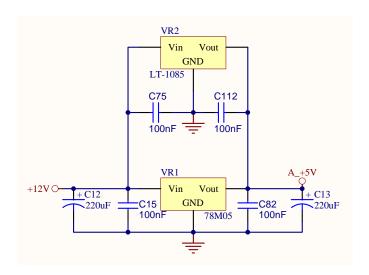

wirken und würden den (S/N) deutlich verschlechtert. Deshalb wird die analoge Versorgungsspannung aus einer unabhängigen +12 V Quelle mit einem Festspannungsregler LT-1085 realisiert. Der LT-1085 deckt mit seinem Ausgangsstrom von bis zu 3 A den gesamten Leistungsbedarf der Analogschaltung ab. Außerdem schafft man durch ihn eine zusätzliche Unterdrückung der Restwelligkeit des speisenden Schaltnetzteils. Die Abbildung 3.7 zeigt die realisierte Spannungsversorgung (+5 V analog). Der zusätzlich vorgesehene Spannungsregler 78M05 ist nur für die Entwicklungsphase ohne Gehäuse notwendig.

Abbildung 3.7: +5 V analoge Spannungsversorgung für AD-Wandler

#### 3.1.1.3 Referenzspannung

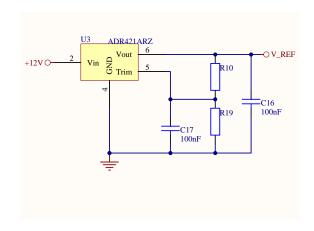

Die Referenzspannung für die Quantisierungsstufe wird von einem hoch genauen »Voltage Reference « Baustein ADR421 abgeleitet und intern auf 4,096V verstärkt. Es ist besonders wichtig, eine möglichst genaue und rauscharme Referenzspannung zu erzeugen, sonst muss man mit Auflösungsverlusten und Ungenauigkeiten rechnen. Die Abbildung 3.8 zeigt die realisierte Referenzspannung mit ihrer externen Beschaltung. Mit Hilfe der beiden Widerstände R10 und R19 kann die Referenzspannung nachge-

Abbildung 3.8: Referenzspannung für AD7674

trimmt werden. Durch die Kondensatoren wird die Spannung stabilisiert und gegen Schwingverhalten geschützt.

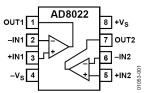

## 3.1.2 Operationsverstärker AD8022

Der eingesetzte Operationsverstärker (OPV) in Abbildung 3.9 soll sich besonders gut für die Realisierung aktiver Filter und ADC-Buffer eignen. Obwohl er für einen 16 Bit AD-Wandler spezifiziert ist, wird er trotzdem vom Hersteller empfohlen. Die Eignung in Hinblick auf die zu realisierende Schaltung und den eingesetzten 18 Bit AD-Wandler soll etwas näher untersucht werden. Die unten angegebene Liste zeigt einige wichtige Eigenschaften des Operationsverstärkers auf, die im Anschluss näher betrachtet werden. Weitere Angaben sind im Datenblatt zu finden.

#### **FUNCTIONAL BLOCK DIAGRAM**

Abbildung 3.9: Blockdiagramm AD8022 (Analog Devices)

- $\bullet$  130 MHz Kleinsignalbandbreite @  $U_{out,ss}=50~\text{mV}$  , G=+1

- ullet 4 MHz Großsignalbandbreite @ U $_{out,ss}=$  4 V, G =+1

- ullet 62 ns Einschwingzeit 0.1 % @ U $_{out.ss}=$  2 V s-s

- Verzerrungen @ ( $U_{out,ss} = 2 \text{ V}, f_c = 1 \text{ MHz}$ )

- 2. Oberschwingung -95 dBc

- 3. Oberschwingung -100 dBc

- ullet 98 dB Gleichtaktstörunterdrückung (CMRR) @ U $_{cm}=$  2.5 V, U $_{s}=\pm5.0$  V

- 80 dB Netzstörunterdrückung (PSRR) @  $U_s = \pm 5V$  bis  $\pm 12~V$

- -77/-82 dB Übersprechen an Ausgängen (Crosstalk) ≤ 10 kHz

Einige nicht ideale Eigenschaften des OPV, wie Offsetstrom und -spannung, spielen bei den meisten Messverfahren im Teleskop Effelsberg keine besondere Rolle. Solche systematischen Fehler können durch Kalibrierung oder Differenzbildung aus den Messdaten entfernt werden und beeinflussen nicht die Messgenauigkeit. Es muss nur garantiert werden, dass sie über die Messperioden konstant bleiben. Weil der AD8022 keine Möglichkeit für Offset-Abgleich bietet, muss es im digitalen Datenstrom verrechnet werden.

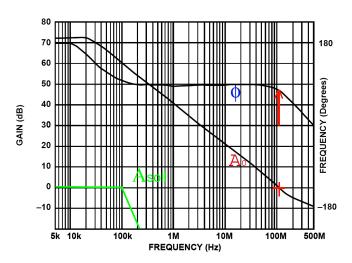

#### 3.1.3 Bandbreite und Frequenzgang

Für einen Tiefpass mit einer Grenzfrequenz von 100 kHz und einer Verstärkung von 0 dB reicht die Bandbreite des AD8022 vollkommen aus. Selbst bei einer Ausgangsspannung von  $U_{out,ss}=4$  V liegt die Grenzfrequenz It. Datenblatt bei 4 MHz. Interessant ist eher das Einschwingverhalten auf Rechtecksignale am Eingang. Das Frequenzspektrum eines Rechtecksignals beinhaltet außer der Grundfrequenz noch eine Vielzahl an ungeradzahligen Oberschwingungen und wird mathematisch wie folgt beschrieben (Gleichung 3.2 (Bartsch 2001, S. 537)).

$$f(t) = \hat{U}\frac{4}{\pi} \left( \sin t + \frac{1}{3}\sin 3t + \frac{1}{5}\sin 5t + \dots \right)$$

(3.2)

Bedenkt man, dass ein ideales Rechtecksignal sich über das gesamte Frequenzspektrum verteilt und Frequenzanteile bei ungeradzahligen Vielfachen der Taktfrequenz hat, dann muss der Operationsverstärken auf seine Eigenschaften etwas näher untersucht werden.

Anhand des Bode-Diagramms in Abbildung 3.10 lässt sich auf einige wichtige Eigenschaften des AD8022 zurückschließen. Mit einer Phasenreserve von ca. 80° bei 0 dB Durchgang, kann die gewünschte Schaltung nie instabil wer-

Abbildung 3.10: Leerlaufverstärkung und Phasengang (Analog Devices)

den. Aufgrund der hohen Phasenreserve, kann man davon ausgehen, dass es auch keine Überhöhung (Gain Peaking) geben wird. Mit Hilfe der Gleichung 3.3 (Aurich 2005, Bauelemente und Elektronik) kann die maximale Überhöhung berechnet werden.

$$\frac{GP}{dB} = -10 \cdot \log[(1 - \cos(\alpha))^2 + \sin(\alpha)^2]$$

(3.3)

$$\frac{GP}{dB} = -10 \cdot \log[(1 - \cos(80^\circ))^2 + \sin(80^\circ)^2] = -2, 18$$

(3.4)

Bei einem negativen Gain Peaking kann man davon ausgehen, dass die Schaltung bei Anregung mit Rechtecksignalen kein Überschwingverhalten zeigt.

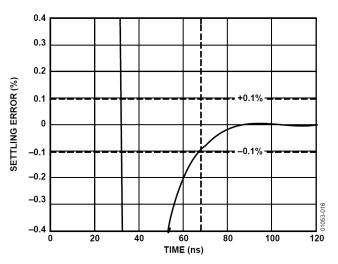

## 3.1.4 Einschwingverhalten

Die Einschwingdauer des Operationsverstärkers ist besonders für sprunghaft ändernde Messsignale von Bedeutung. In der Testschaltung von »Analog Devices « mit einer Verstärkung von G = +2 wird eine Genauigkeit von 99,9 % bereits nach 68 ns erreicht, bei einer Verstärkung von G = +1 bereits nach 62 ns. Wie bereits erwähnt, zeigt der Operationsverstärker kein nennenswertes Überschwingverhalten (Abbildung 3.11). Auch wenn es noch nicht auf das letzte Bit genau ist, so kann man davon ausgehen, dass der OPV innerhalb weniger Abtastwerte seinen Endwert erreicht und bei weitem schnel-

Figure 16. Settling Time to 0.1%,  $V_S = \pm 12 \text{ V}$ , Step Size = 2 V p-p, G = +2,  $R_L = 500 \Omega$

Abbildung 3.11: Einschwingverhalten @ G = +2 (Analog Devices)

ler ausregelt als der zu realisierende Tiefpass.

## 3.1.5 Nichtlineare Verzerrungen

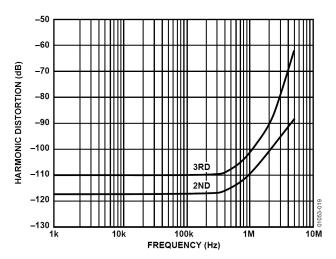

Nichtlineare Verzerrungen können beispielsweise im Frequenzbereich untersucht werden. Durch nichtlineare Verzerrungen entstehen aus einem Sinussignal am Eingang zusätzliche Oberschwingungen am Ausgang. Anders ausgedrückt kann man sagen, dass die Verstärkung über den Aussteuerungsbereich nichtlinear verläuft. Die Abbildung 3.12 zeigt die dadurch entstehenden Anteile der zweiten und dritten Oberschwingung eines Sinussignals. Bei einer Aussteuerung von  $\pm 2V$  erreicht

Distortion vs. Frequency,  $V_S = \pm 12 \text{ V}$ ,  $R_L = 500 \Omega$ ,  $R_F = 0 \Omega$ ,  $V_{OUT} = 2 \text{ V p-p}$ , G = +1

Abbildung 3.12: Distortion vs. Frequency (Analog Devices)

der AD8022 eine Pegeldifferenz zu der zweiten Oberschwingung von bis zu 110 dBc. Bei gleich bleibender Eingangsspannung steigt die Verzerrung lt. Datenblatt mit fallender Versorgungsspannung an. Deshalb ist eine möglichst hohe Versorgungsspannung zu empfehlen. Eine geringfügige Erhöhung der nichtlinearen Verzerrung durch die Verwendung der beiden OPV ist möglich. Bei einer Verdoppelung der Verzerrung würde die Pegeldifferenz um 6 dB fallen. Für den eingesetzten AD-Wandler mit einem Dynamikbereich von 103 dB sollte bei einer Eingangsbandbreite von 100 kHz kein nennenswerter Verzerrungsanteil entstehen.

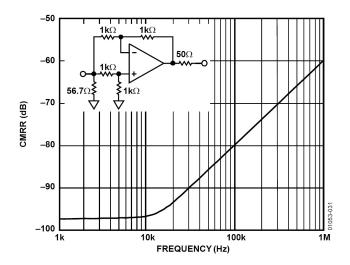

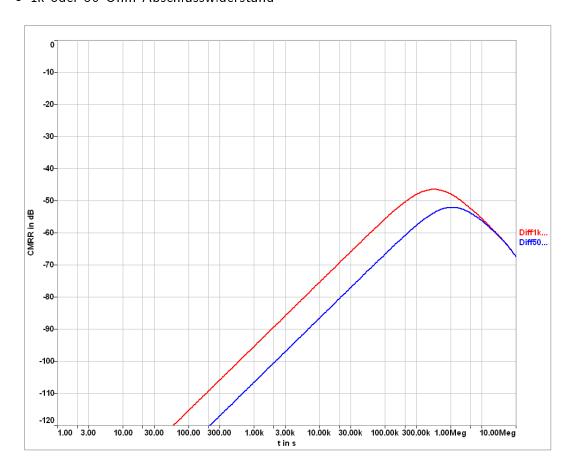

### 3.1.6 Gleichtaktstörunterdrückung CMRR

Die Gleichtaktstörunterdrückung der einzelnen Operationsverstärker zeigt hervorragende Wirkung und würde normalerweise für die Anwendung vollkommen reichen (Abbildung 3.13). Gerade Störungen im NF-Bereich wie Netzspannung werden mit 98 dB unterdrückt und selbst bei der gewünschten Grenzfrequenz von 100 kHz wäre immer noch eine Dämpfung von 80 dB. Für die Realisierung der differentiellen Ein- und Ausgänge werden aber beide Operationsverstärker im AD8022 benötigt. Aufgrund von Bauteiltoleranzen der beiden

Abbildung 3.13: CMRR vs. Frequency (Analog Devices)

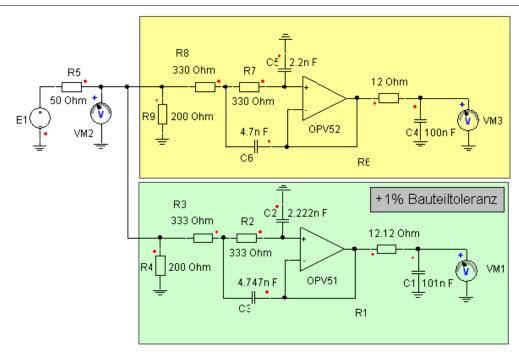

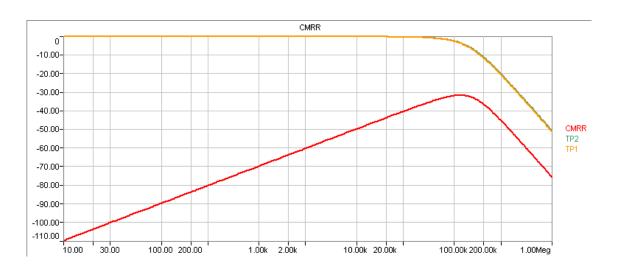

Operationsverstärker und der RC-Glieder erhöht sich die Gleichtaktempfindlichkeit der Schaltung und entspricht nicht mehr dem CMRR eines einzelnen OPV. Daher ist die Verwendung von Bauteilen mit möglichst geringer Toleranz von großer Bedeutung. Im Augenblick sind die Auswirkungen unbekannt und können erst nach dem Fertigstellen des Gerätes untersucht werden. Mit Hilfe der Simulationsschaltung in Abbildung 3.14 auf der nächsten Seite kann aber der erste Eindruck gewonnen werden.

Abbildung 3.14: Simulationsschaltung

Bei einer Bauteiltoleranz von +1 % der passiven Bauelemente entsteht nach Abbildung 3.15 folgende Gleichtaktstörunterdrückung. Mit steigender Frequenz vergrößert sich die Differenz im Amplituden- und Phasengang der beiden Filter und sorgt für eine Differenzspannung am Ausgang. Erst nach 100 kHz ist ein erneuter Dämpfungsanstieg zu beobachten, der durch das Tiefpassverhalten verursacht wird.

Abbildung 3.15: Simulation der Gleichtaktstörunterdrückung

## 3.1.7 Versorgungsspannung

Weitere wichtige Parameter sind die Versorgungsspannung und die Netzstörunterdrückung (PSRR). Bei hoher Versorgungsspannung erreicht man lt. Datenblatt in den meisten Fällen bessere Ergebnisse. Die Auslegung der Versorgungsspannung richtet sich nach der gewünschten Ausgangsspannung. Für einen Aussteuerungsbereich von 0 V bis 4,096 V muss eine symmetrische Versorgungsspannung verwendet werden, damit auch um die Nulllinie keine nichtlinearen Verzerrungen entstehen. Bei der gewünschten Großsignal-Aussteuerung sollte eine Spannung von  $\pm 9$  bis  $\pm 12$  V reichen.

Die Abbildung 3.16 zeigt die Netzstörunterdrückung des AD8022 über der Frequenz. Nur im unteren Frequenzbereich wird eine hohe Störunterdrückung erreicht, die mit steigender Frequenz deutlich nachlässt und nahezu gegen Null geht. Störungen in der Versorgungsspannung durch verwendete Schaltnetzteile und andere Baugruppen wie FPGA und Ethernet sind nicht auszuschließen und müssen ausreichend unterdrückt werden. Eine effektive Entstörung und Entkopplung der Versorgungsspannungen wird in Kapitel 4 auf Abbildung 3.16: Netzstörunterdrückung vs. Seite 43 näher beschrieben.

Power Supply Rejection vs. Frequency  $V_S = \pm 12 V$

Frequenz (Analog Devices)

#### 3.1.8 Crosstalk

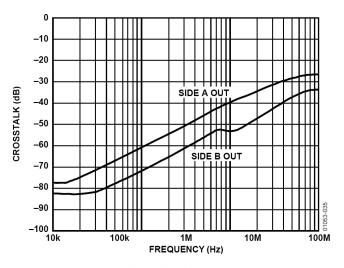

Durch die Verwendung von beiden Operationsverstärkern in einem Gehäuse lässt sich Kanalübersprechen nicht vermeiden. Die Abbildung 3.17 auf der nächsten Seite zeigt das Übersprechen der beiden Kanäle in Abhängigkeit von der Frequenz. Für die Messsignale ist eigentlich nur der untere Frequenzbereich von Bedeutung. Bedenkt man, dass die Ansteuerung der beiden OPV in entgegengesetzte Richtung erfolgt, dann muss mit einer starken Abweichung an beiden Ausgängen gerechnet werden. Bei einem Cross-Talk von 82 dB Abstand erreicht man gerade mal die notwendige Genauigkeit für einen 13 bis 14 Bit AD-Wandler.

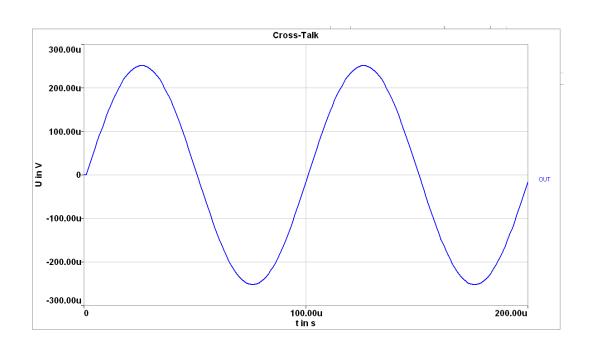

Dieser systematische Fehler lässt sich auch durch Differenzbildung nicht kompensieren und muss durch eine Multiplikation mit einem Faktor korrigiert werden. Dies setzt jedoch voraus, dass die beiden Ausgängen absolut symmetrisch angesteuert werden und der Offset am Eingang konstant bleibt, weil am Ausgang nur die Differenz gemessen werden kann und das Übersprechen der beiden Ausgänge nicht identisch ist. Die Abbildung 3.18 zeigt das Ergebnis einer Simulation des Übersprechens von OUT-B nach OUT-A bei einer Eingangsspannung von  $\mathbb{U}_{ss}=2~\mathrm{V}.$

Output-to-Output Crosstalk vs. Frequency,  $V_S = \pm 12 V$

Abbildung 3.17: Output-to-Output Crosstalk vs. Frequency(Analog Devices)

Abbildung 3.18: Cross-Talk im AD8022

Wie man dem Simulationsergebnis entnehmen kann, entsteht bei einem Crosstalk von -78 dB bereits eine Spannung von 250  $\mu$ V, die eine Abweichung von 8 LSB verursacht. Bei einer symmetrischen Ansteuerung der beiden OPV würde eine Abweichung von 13 LSB entstehen.

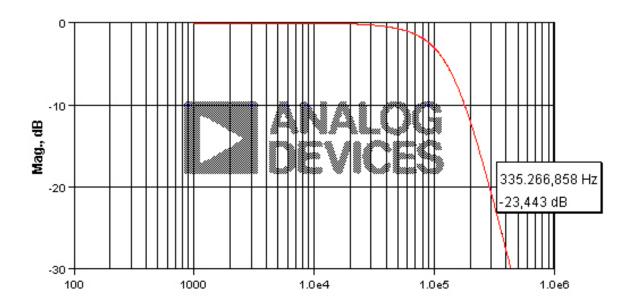

# 3.2 Frequenzgang des Anti-Aliasing-Filters

Die festgelegte Grenzfrequenz von 100 kHz liegt zwar deutlich unter der halben Abtastrate, reicht aber für die Unterdrückung aller Aliasing-Effekte bei weitem nicht aus. Bei einem Abfall von ca. 60 dB/dec erreicht das Filter bei einer Nyquist-Frequenz von ca. 333 kHz gerade mal eine Dämpfung von 23 dB (Abbildung 3.19). Für den eingesetzten 18 Bit AD-Wandler wäre bei der genannten Nyquist-Fequenz eine Dämpfung von über 100 dB nötig. Die verwendete Schaltung erreicht erst bei einer Frequenz von ca. 10 MHz die notwendige Dämpfung. Für das Eingangssignal bedeutet es aber, dass es keine nennenswerten Störanteile über der Nyquist-Frequenz beinhaltet darf.

Abbildung 3.19: Frequenzgang der analogen Eingangsstufe

# 3.3 Eingangswiderstand

Im Idealfall sollte der Eingangswiderstand dem Ausgangswiderstand der Quelle und der Leitungsimpedanz von 50  $\Omega$  entsprechen. Durch die Impedanzanpassung werden Reflexionen und Überschwingungen vermieden und die abgestrahlte Leistung minimiert. Der niedrige Eingangswiderstand macht auch die Eingangsstufe deutlich unempfindlicher gegen hochohmige Störquellen und verbessert den Signal-Störabstand. Zusätzlich wird die Einschwingdauer

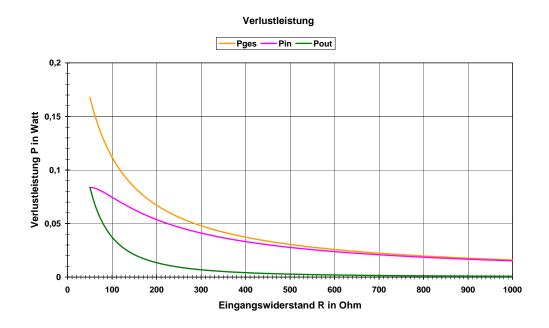

der vorgeschalteten EMI-Filter verkürzt (siehe Abschnitt 3.22). Aufgrund der hohen Verlustleistung, die bei einem 50 Ohm Eingangswiderstand entstehen würde, wird zunächst ein Eingangswiderstand zwischen 100 und 500 Ohm verwendet. Mit Hilfe der Gleichungen 3.5 bis 3.6 wurden die Verlustleistungen bei einer Quellenspannung von 4,096 V berechnet und im Diagramm 3.20 dargestellt.

$$P_{ges} = \frac{U^2}{(R_{out} + R_{in})} \tag{3.5}$$

$$P_{R_{out,50}} = \frac{U^2 \cdot R_{out,50}}{(R_{out,50} + R_{in})^2}$$

(3.6)

$$P_{R_{in}} = \frac{U^2 \cdot R_{in}}{(R_{out,50} + R_{in})^2} \tag{3.7}$$

Abbildung 3.20: Verlustleistung

Je nach Auswahl der Widerstände sollte der Aussteuerungsbereich angepasst werden. Mit jedem nicht genutzten MSB verliert man ca. 6 dB an Signal-Rauschabstand.

# 3.4 Ausgangswiderstand der Schaltung

Die hohe Versorgungsspannung von  $\pm 12$  V stellt im Fehlerfall oder bei hoher Eingangsspannung eine Gefahr für die gesamte Schaltung dar. Weil die Eingangswiderstände des AD-Wandlers hinter den Schutzdioden sitzen, muss der Strom durch den Ausgangswiderstand der Filterschaltung begrenzt werden. Bei der Festlegung des Vorwiderstandes ist zu berücksichtigen, dass ein zu hoher Wert einen Einfluss auf die Auf- und Entladungszeit des S&H-Kondensators (Sample und Hold) hat und lt. Datenblatt sich die Verzerrungen erhöhen. Deshalb wurde der minimale Ausgangswiderstand nach dem schwächsten Glied berechnet.

- Der AD8022 ist eigentlich kurzschlussfest und hat einen max. Ausgangsstrom von 100

mA, erreicht aber je nach Versorgungsspannung eine unzulässig hohe Verlustleistung.

- Die Schutzdioden des AD-Wandlers haben eine max. Strombelastbarkeit von 120 mA.

Damit sollte es bei kurzzeitigem Übersteuern zu keiner direkten Zerstörung führen und ein Vorwiderstand wäre überflüssig.

- Bei längerer Belastung in positive Richtung ist eine max. Verlustleistung am AD8022 von

$$P_v = (12 - 5 - 0.5)V \cdot 0.1A = 0.65W \tag{3.8}$$

zu erwarten. Bei dem verwendeten SOIC-Package darf bei dieser Verlustleistung eine max. Umgebungstemperatur von ca. 60 °C nicht überschritten werden. Bei einer ausreichenden Kühlung, sollte keine Gefahr für die Bauteile bestehen.

Bei längerer Belastung in negative Richtung ist eine max. Verlustleistung am AD8022 von

$$P_v = (12 - 0.5)V \cdot 0.1A = 1.15W \tag{3.9}$$

zu erwarten. Um eine Verlustleistung von 1,15 W sicher abführen zu können, darf eine Umgebungstemperatur von -10°C nicht überschritten werden. Bei einem Wärmewiderstand  $\Theta_{JA}=160$  °C/W und normaler Raumtemperatur wird die max. zulässige Sperrschichttemperatur überschritten und der AD8022 zerstört.

- Der im Augenblick ausgelegte Vorwiderstand von 36  $\Omega$  (R2 und R6) muss im Extremfall eine Verlustleistung von 0,36 W vertragen. Die eingesetzten 0805 SMD-Widerstände haben eine max. Verlustleistung von 125 mW und würden die Belastung nicht aushalten.

- ullet Ein Vorwiderstand von 12 bis 15  $\Omega$  hätte eine Verlustleistung von ca. 150 mW und würde bei einer ausreichenden Kühlung es aushalten. Vorsichtshalber kann man die

Widerstände aus der 1206-Baugröße verwenden. Der AD8022 hätte dann eine Verlustleistung von

$$P_v = (12 - 1, 5 - 0, 5)V \cdot 0.1A = 1W \tag{3.10}$$

was eine direkte Zerstörung vermeiden würde. Es wird aber eine gute Kühlung der Widerstände und des OPV vorausgesetzt.

Um den Tiefpass nicht zu verändert, wird eine neue Kapazität nach Gleichung 3.11 berechnet.

$$C_{neu} = \frac{R_{alt} \cdot C_{alt}}{R_{neu}} \approx 100nF \tag{3.11}$$

• Die beste Lösung wäre statt  $\pm 12$  V nur  $\pm 9$  V zu verwenden.

### 3.5 Fazit

Laut den vorgenommenen Untersuchungen reicht die Genauigkeit des Operationsverstärkers wegen des starken Crosstalks für einen 18 Bit AD-Wandler bei weitem nicht aus, auch wenn der Hersteller den AD8022 als Lösung für differentielle Eingangssignale empfiehlt. Ohne zusätzlichen Abgleich und Korrektur der Messdaten muss man sich bei Vollaussteuerung mit ca. 13 bis 14 Bit Genauigkeit begnügen. Wegen der Toleranz der beiden Filter müssen auch Gleichtaktstörungen unbedingt vermieden werden, z.B. durch gut abgeschirmte Leitungspaare und impedanzarme Masseverbindungen. Auch wegen der geringen Dämpfung bei der Nyquist-Frequenz können Aliasing-Effekte nicht vermieden werden und müssen bereits in der Signalquelle unterdrückt sein. Der einzige Vorteil des 18 Bit AD-Wandler liegt in seinem hohen Dynamikbereich und Signal-Rauschabstand von ca. 100 dB. Damit ermöglicht er die Realisierung eines besonders empfindlichen Eingangs und macht eine Differenzmessung bereits ab 31,25  $\mu$ V (1LSB) möglich. Um die volle Auflösung des AD-Wandlers nutzen zu können, muss in Zukunft ein anderer Operationsverstärker verwendet werden. Es ist zu empfehlen einen echten Differenzverstärker oder sogar Instrumentenverstärker zu verwenden. Die Abbildung 3.21 auf der nächsten Seite zeigt die leicht modifizierte Eingangsstufe.

Abbildung 3.21: Modifizierte analoge Eingangsstufe

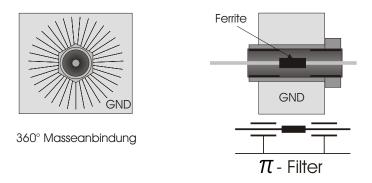

## 3.6 EMI-Filter - Tusonix 4209-053

Mit Hilfe der EMI¹-Filter sollen alle I/O-Schnittstellen sowie Spannungsversorgungen möglichst breitbandig entstört werden. Die Besonderheit solcher Durchgangsfilter liegt in ihrer Bandbreite und hohen Strombelastbarkeit. Eine Dämpfung von 60 dB und mehr ist selbst bei 10 GHz möglich. Die hohe Entstörbandbreite erreicht man durch die radiale Form und direkte Masseanbindung mit geringer Induktivität (Abbildung 3.22). Allein schon aus diesem Grund kommt ein Gehäuse aus Stahl nicht in Frage. Die Impedanz von Stahl steigt sehr stark mit der Frequenz an.

Abbildung 3.22: Masseanbindung und Aufbau vom EMI-Filter

<sup>&</sup>lt;sup>1</sup>elektromagnetische Interferenz

Das zum Einsatz kommende EMI-Filter Tusonix 4209-053 wurde nach folgenden Kriterien ausgesucht (Tabelle 3.1).

Tabelle 3.1: Auswahlkriterium für EMI-Filter

| Auswahlkriterium        | Bewertung | Bemerkung                                 |  |  |  |  |

|-------------------------|-----------|-------------------------------------------|--|--|--|--|

| Verfügbarkeit sehr hoch |           | Eine kurzfristige Beschaffung und geringe |  |  |  |  |

|                         |           | Stückzahl stellt bei vielen Typen ein     |  |  |  |  |

|                         |           | Problem dar.                              |  |  |  |  |

| Frequenzgang hoch G     |           | Große Entstörbandbreite und Dämpfung      |  |  |  |  |

|                         |           | bis in den Gigahertz-Bereich.             |  |  |  |  |

|                         |           | Schnelles Einschwingverhalten. Ein        |  |  |  |  |

|                         |           | Kompromiss zwischen unterer               |  |  |  |  |

|                         |           | Grenzfrequenz und Einschwingdauer.        |  |  |  |  |

| Größe                   | mittel    | Hohe Packungsdichte. Es werden ca. 80     |  |  |  |  |

|                         |           | Filter benötigt.                          |  |  |  |  |

| Filterordnung           | hoch      | z.B. PI-Filter 3. Ordnung mit starkem     |  |  |  |  |

|                         |           | Abfall.                                   |  |  |  |  |

## 3.6.1 Frequenzgang

Im Datenblatt des Herstellers ist keine genaue Frequenzkennlinie vorhanden und nur an wenigen Stellen eine Dämpfung angegeben (Tabelle 3.2).

Tabelle 3.2: Minimum no load insertion loss (Tusonix 4209-053)

| Frequenz in GHz | Dämpfung in |  |  |  |

|-----------------|-------------|--|--|--|

|                 | dB          |  |  |  |

| 0.01            | 20          |  |  |  |

| 0.1             | 65          |  |  |  |

| 1               | 70          |  |  |  |

| 10              | 70          |  |  |  |

Die Dämpfung steigt bis zu 70 dB an und zeigt selbst bei 10 GHz noch keinen Abfall. Damit sollten hochfrequente Störungen von den schnellen Digitalschaltungen wie Ethernet und FPGA unterdrückt werden können. Für analoge Eingangssignale bis 100 kHz stellt das Filter keine bemerkenswerte Bandbreitenbegrenzung dar.

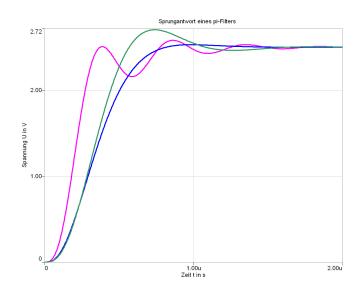

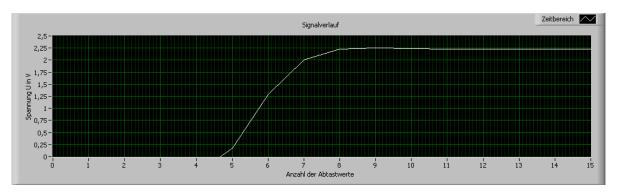

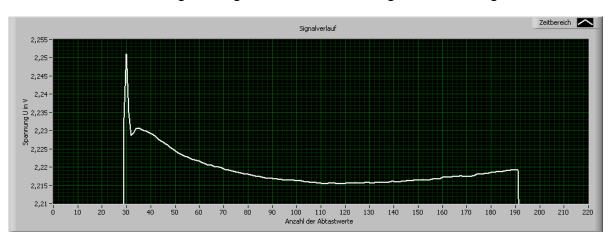

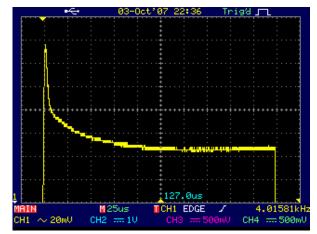

### 3.6.2 Sprungantwort

Besonders wichtig ist die Sprungantwort des Filters. Es muss ein Kompromiss zwischen der unteren Grenzfrequenz und der Einschwingdauer gefunden werden. Langes Einschwingverhalten würde die BLANK-Zeit vergrößern und damit die Beobachtungsdauer verkürzen. Eine zu hohe Grenzfrequenz lässt dagegen Störungen im unteren Frequenzbereich durch. Betrachtet man in Abbildung 3.23 einige Einschwingvarianten, so stellt man fest, dass sie zwar alle nach ungefähr der gleichen Zeit ihren Endwert erreichen, aber ein

Abbildung 3.23: Einschwingverhalten von pi-Filtern

sehr unterschiedliches Einschwingverhalten zeigen.

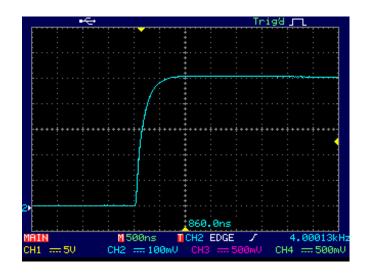

Wegen mangelnder Angaben vom Hersteller kann keine genaue Übertragungsfunktion aufgestellt werden. Deshalb wird durch messtechnisches Verfahren das Einschwingverhalten untersucht. Dabei wird ein Rechtecksignal aufgeschaltet und am Filterausgang mit einem Oszilloskop aufgezeichnet. Die Ein- und Ausgangswiderstände sind identisch und betragen 50 Ohm. Wie man der Abbildung 3.24 entnehmen kann, zeigt die Sprungantwort kein Überschwingverhalten und erreicht ihren Endwert nach ca. 1  $\mu$ s.

Abbildung 3.24: Sprungantwort des EMI-Filters Tusonix 4209-053

## 3.6.3 Gleichtaktstörung

Ein zusätzlicher Nachteil entsteht bei Verwendung von Durchgangsfiltern für differentielle Signale. Durch Bauteiltoleranz der Filter erhöht sich die Empfindlichkeit für Gleichtaktstörungen. Eine einfache Simulation soll das Problem verdeutlichen. Die Auflistung zeigt die wichtigsten Simulationsparameter:

- Störung in der Quelle mit 50 Ohm Ausgangswiderstand

- $\bullet$  Simulationsmodel des 4209-53 mit  $T_{63} \approx 180$  ns

- Bauteiltoleranz an jedem Glied ca. 10 %

- 1k oder 50 Ohm Abschlusswiderstand

Abbildung 3.25: Entstandene Differenzspannung durch Bauteiltoleranz

Wie man dem Simulationsergebnis in Abbildung 3.25 entnehmen kann, macht sich eine Bauteiltoleranz von 10 % schon deutlich bemerkbar. Durch Verwendung von kleineren Eingangswiderständen kann die Empfindlichkeit reduziert werden. Besonders problematisch ist

der Bereich, in dem weder das EMI-Filter noch die Eingangstufe eine ausreichende Dämpfung bietet. Störungen um die 100 kHz können das EMI-Filter und die Eingangsstufe problemlos passieren.

#### 3.6.4 Zusammenfassung

Aufgrund der mangelnden Auflösung eines Oszilloskops kann weder die Signalverformung noch das Gleichtaktverhalten näher untersucht werden. Auch die Simulation kann keine genauen Aussagen darüber machen. Man kann aber davon ausgehen, dass die analoge Eingangsstufe einen deutlich höheren Einfluss auf die Signalverzerrung und Gleichtaktempfindlichkeit hat und die EMI-Filter zu vernachlässigen sind.

## 3.7 Digitalschaltung

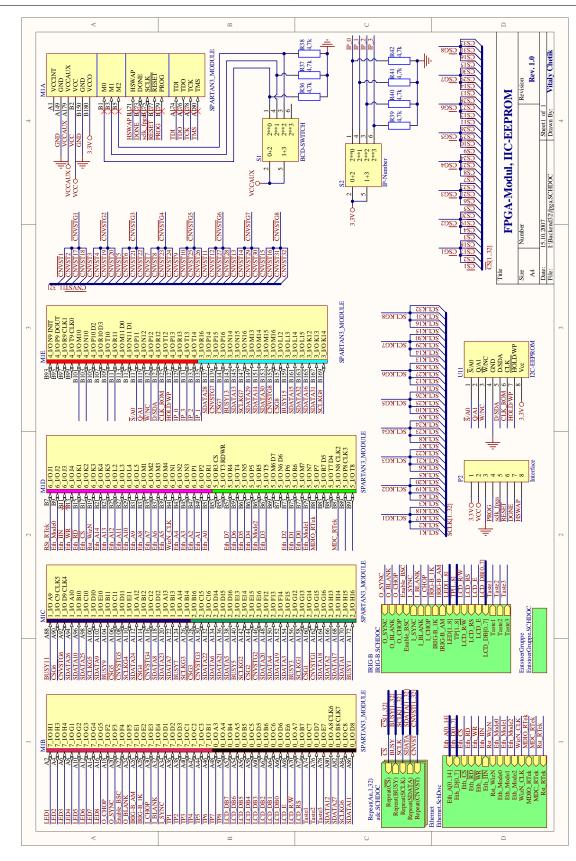

Das Blockschaltbild 3.26 gibt einen Überblick über die entwickelte digitale Hardware des Backends, mit der alle notwendigen Funktionen abgedeckt werden können. In den einzelnen Abschnitten wird je nach Schaltungsaufwand ausführlicher drauf eingegangen. Der gesamte Schaltplan zu der Hardware sowie die Datenblätter sind im Anhang A und Anhang B zu finden.

Abbildung 3.26: Blockschaltbild zur digitalen Hardware

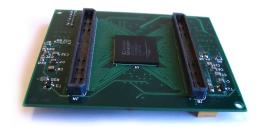

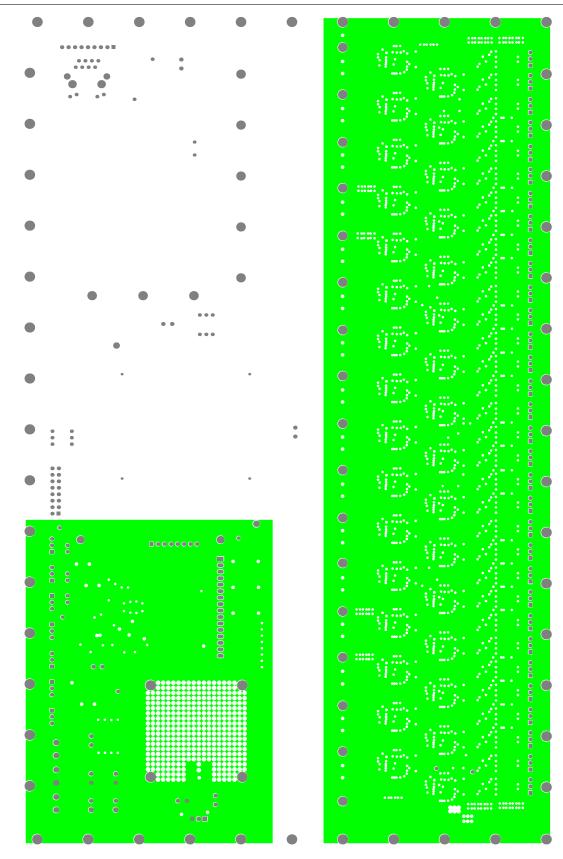

#### 3.7.1 FPGA-Modul

Das Hauptelement und Herzstück der gesamten Schaltung stellt ein FPGA dar. Zum Einsatz kommt ein Xilinx-FPGA der Spartan-3 Familie. Es bietet eine ausreichende Anzahl an Logik, Multiplizierer und Block-RAM. Damit kann die gesamte Steuerung, Signalverarbeitung und Datenübertragung realisiert werden. Um die Entwicklungszeit und Fehlerquellen zu minimieren wurde ein fertiges FPGA-Modul aus dem Digitallabor entnommen. Das bereits erprobte und mehrfach eingesetzte FPGA-Modul beinhaltet alle Bauteile, die für den Betrieb des FPGAs erforderlich sind. Dazu gehören mehrere Schaltnetzteile, EERPOM und Interface für die Konfiguration und ein paar Test-LEDs. Das Modul kann mit drei unterschiedlich komplexen FPGA-Typen bestückt werden und ermöglicht einen universellen Einsatz. Ein zusätzlicher Vorteil ist die Reduzierung der Lagenanzahl auf der Hauptplatine, weil die Versorgungsspannungen für das FPGA auf dem Modul realisiert werden. Die Abbildung 3.27 und 3.28 zeigen das verwendete FPGA-Modul.

Abbildung 3.27: FPGA-Modul (Top)

Abbildung 3.28: FPGA-Modul (Bottom)

Um den gesamten Umfang an Steuerung und Signalverarbeitung abdecken zu können, wurde das Modul mit dem größtmöglichen SPARTAN-3/1000 bestückt. Die Tabelle 3.29 auf der nächsten Seite gibt eine kurze Übersicht über die Spartan-3 Familie.

| Spartan-3                  | XC<br>3S50 | XC<br>3S200 | XC<br>3S400 | XC<br>3S1000 | XC<br>3S1500 | XC<br>3S2000 | XC<br>3S4000 | XC<br>3S5000 |

|----------------------------|------------|-------------|-------------|--------------|--------------|--------------|--------------|--------------|

| System Gates               | 50K        | 200K        | 400K        | 1000K        | 1500K        | 2000K        | 4000K        | 5000K        |

| Logic Cells                | 1,728      | 4,320       | 8,064       | 17,280       | 29,952       | 46,080       | 62,208       | 74,880       |

| 18x18 Multipliers          | 4          | 12          | 16          | 24           | 32           | 40           | 96           | 104          |

| Block RAM Bits             | 72K        | 216K        | 288K        | 432K         | 576K         | 720K         | 1,728K       | 1,872K       |

| Distributed RAM Bits       | 12K        | 30K         | 56K         | 120K         | 208K         | 320K         | 432K         | 520K         |

| DCMs                       | 2          | 4           | 4           | 4            | 4            | 4            | 4            | 4            |

| I/O Standards              | 24         | 24          | 24          | 24           | 24           | 24           | 24           | 24           |

| Max Differential I/O Pairs | 56         | 76          | 116         | 175          | 221          | 270          | 312          | 344          |

| Max Single Ended I/O       | 124        | 173         | 264         | 391          | 487          | 565          | 712          | 784          |

| Package                    | User       | User        | User        | User         | User         | User         | User         | User         |

|                            | I/O        | I/O         | I/O         | I/O          | I/O          | I/O          | I/O          | I/O          |

| VQ100                      | 63         | 63          | -           | -            | _            | -            | -            | -            |

| TQ144                      | 97         | 97          | 97          | -            | -            | -            | -            | -            |

| PQ208                      | 124        | 141         | 141         | _            | -            | _            | -            | -            |

| FT256                      | -          | 173         | 173         | 173          | _            | -            | -            | -            |

| FG320                      | _          | -           | 221         | 221          | 221          | _            | -            | -            |

| FG456                      | -          | -           | 264         | 333          | 333          | 333          | -            | -            |

| FG676                      | -          | _           | -           | 391          | 487          | 489          | 489          | 489          |

| FG900                      | _          | -           | -           | -            | _            | 565          | 633          | 633          |

| FG1156                     | -          | -           | -           | -            | -            | -            | 712          | 784          |

Abbildung 3.29: Übersicht zur Spartan-3 Familie (Xilinx Spartan-3 Overview)

Noch ein Vorteil des FPGA-Moduls ist das integrierte 3,3 V Schaltnetzteil, das mit einem Ausgangsstrom von bis zu 3 A den gesamten Leistungsbedarf aller digitalen Bausteine abdeckt.

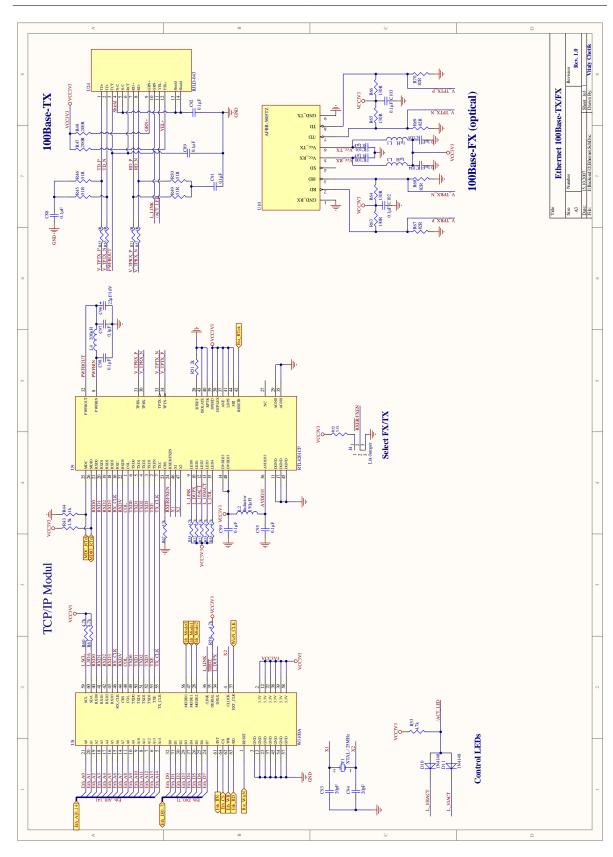

#### 3.7.2 Ethernet

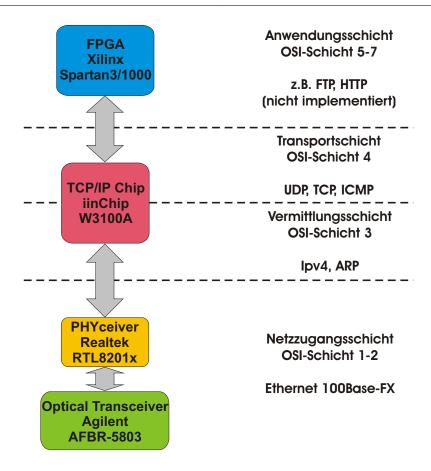

Wie schon in Kapitel 2 erwähnt, wurde für die Datenübertragung eine 100Base-FX Schnittstelle entwickelt. Aus Kompatibilitätsgründen wurde auch die 100Base-TX Schnittstelle realisiert. Die eingesetzte Hardware deckt nahezu den gesamten Bereich des TCP/IP-Referenzmodells ab und reduziert damit den Programmieraufwand im FPGA. Die Abbildung 3.30 auf der nächsten Seite zeigt die verwendete Hardware und die dazugehörenden OSI- und TCP/IP-Schichten. Auf eine nähere Erläuterung des OSI- und TCP/IP-Referenzmodells wird an dieser Stelle verzichtet. Eine ausführliche Beschreibung kann zahlreicher Literatur entnommen werden.

Abbildung 3.30: Ethernet

#### 3.7.2.1 Ethernet-Controller iinChip W3100A

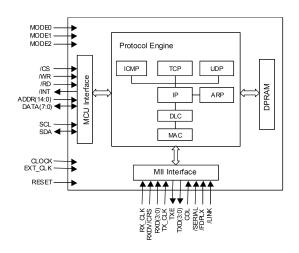

Der W3100A ist ein intelligenter Ethernet-Controller, der einem die Entwicklung der Transport- und Vermittlungsschicht erspart. Das Blockdiagramm 3.31 stellt die externen Schnittstellen dar und verdeutlicht die Komplexität des Chips. Der einzige Nachteil liegt in seiner geringen Datenübertragungsrate. Mit einer Datenrate von ca. 25 Mbit/s wird die 100Base-TX/FX Verbindung bei weitem nicht ausgenutzt. Für das angewendete Messverfahren reicht allerdings die Datenrate vollkommen aus. Während der

Abbildung 3.31: Blockdiagramm W3100A

Entwicklungs- und Testphase können die Rohdaten eines einzelnen AD-Wandlers in Echtzeit übertragen werden.

Die Kommunikation mit dem FPGA wurde über die Parallelschnittstelle realisiert. Die einfache Handhabung und bestehende VHDL-Module waren die ausschlaggebenden Argumente für die Parallelschnittstelle. Die nicht verwendete I2C-Schnittstelle muss über Pullup-Widerstände in einen definierten High-Zustand versetzt werden.

Die Anbindung an einen Physical Layer Chip erfolgt über das Media Independent Interface (MII). Das MII ist eine standardisierte Schnittstelle zwischen Netzzugang (Physical Layer Chip) und der oberen Vermittlungsschicht (MAC). Wie der Name schon sagt, ist an dieser Stelle das tatsächlich verwendete Übertragungsmedium ohne Bedeutung. Der Schaltplan zu der entwickelten Schaltung ist im Anhang A.2 zu finden.

### 3.7.2.2 Physical Layer Chip - Realtek RTL8201

Für die Leitungscodierung und Ansteuerung des Transceivers wurde ein gängiger Physical Layer Chip von Realtek verwendet. Die Entscheidung für den RTL8201 lag zum einen an der einfachen Konfiguration per »hardwire« und zum anderen in der Unterstützung des 100Base-FX Standards. Je nach Konfiguration kann der Chip für den 10/100Base-TX oder 100Base-FX Netzzugang verwendet werden. Die Kommunikation mit der oberen Vermittlungsschicht wird über das bereits genannte MII-Interface abgewickelt. Die elektrische Anbindung an den optischen Transceiver (100Base-FX) oder Übertrager (100Base-TX) wird über zwei Leitungspaare TPRX+/TPRX- und TPTX+/TPTX- realisiert. In beiden Fällen werden die Daten direkt im Basisband übertragen. Der wesentliche Unterschied der beiden Standards liegt in der Leitungscodierung, auf die etwas näher eingegangen wird. Die genau Verdrahtung zum iinChip und FPGA sowie die »Hardwire-Konfiguration« des Chips kann dem Schaltplan im Anhang A.2 entnommen werden.

### 3.7.2.3 100Base-TX Leitungscodierung

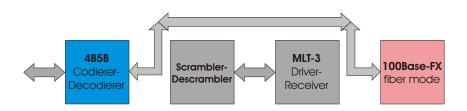

Die Abbildung 3.32 auf der nächsten Seite zeigt den Signalweg bei Übertragung mit Twistedpair-Leitung. Der 4B5B-Codierer verhindert lange 1- und 0-Folgen und vereinfacht die Bitsynchronisation am Empfänger. Der Scrambler sorgt für eine reichliche Verwürfelung der Daten und eine gleichmäßige Verteilung im Spektrum. Durch die breitbandige Verteilung im Spektrum erreicht man zum einen die Unterdrückung starker diskreter Störer und zum anderen eine deutlich unempfindlichere Datenübertragung gegen ext. Störer. Der nachfolgende

MLT-3 Leitungscodierer reduziert durch die ternär codierten Signale die Bandbreite auf ca. 31,25 MHz.

Abbildung 3.32: Signalweg für Twisted-Pair Übertragung (100Base-TX)

Das Ergebnis ist eine ungestörte Datenübertragung mit geringer Bandbreite und zusätzlicher Gleichspannungsfreiheit am Übertager, der sonst in die Sättigung gehen würde.

## 3.7.2.4 100Base-FX Leitungscodierung

Bei der optischen Übertragung in Abbildung 3.33 spielt die Verteilung im Spektrum keine Rolle, deshalb wird der Scrambler auch nicht verwendet. Eine optische ternäre Codierung mit »U+, 0, U-« lässt sich nur schwer realisieren, deshalb kann die Bandbreite nicht reduziert werden. Der Datenstrom wird direkt nach dem 4B5B-Codierer abgegriffen und über optische Transceiver gesendet.

Abbildung 3.33: Signalweg bei optischer Übertragung (100Base-FX)

Wegen der deutlich höheren Baudrate wird statt TTL-Logik die PECL-Logik² verwendet. Die hohe Schaltgeschwindigkeiten der PECL wird erreicht, indem man die Transistoren nicht in die Sättigung treibt. Allerdings entsteht dadurch eine deutlich höhere Verlustleistung. Die ext. Beschaltung mit den beiden Widerständen sorgt für definierte Pegel am Ausgang und ergibt im Kleinsignalverhalten ca. 50  $\Omega$  Lastwiderstand (82||130) (Abbildung 3.36 auf Seite 35).

<sup>&</sup>lt;sup>2</sup>Positive emitter-coupled logic

### 3.7.2.5 Optical Transceiver - Agilent AFBR-5803ATZ

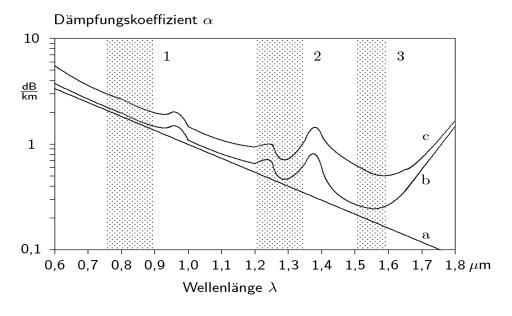

Aus der Vielzahl an angebotenen Transceivern konnte der AFBR-5803ATZ in Abbildung 3.34 allen Ansprüchen gerecht werden. Er wurde speziell für Fast Ethernet, FDDI und ATM entwickelt und überwindet eine Strecke von bis zu 2 km. Damit kann man auf einen zusätzlichen Repeater in der Übertragungsstrecke verzichten. Die eingesetzte LED und PIN-Photodiode arbeiten im 2. Übertragungsfenster des Lichtwellenleiters, dem sogenannten O-Band, bei einer Wellenlänge von 1300 nm (Abbildung 3.35). Damit ist der Transceiver

Abbildung 3.34: Optical Transceiver - Agilent AFBR-5803ATZ

vollkompatibel zu allen anderen 100Base-FX Schnittstellen. Als Gegenstelle kann ein einfacher 100Base-FX Ethernetadapter verwendet werden.

Abbildung 3.35: Übertragungsfenster und Dämpfungsverlauf einer Gradientenfaser (c), einer Einmodenfaser (b) und minimaler Grenzwert des Lichtwellenleiters [Haaß, 2005]

### 3.7.2.6 Elektrische Schnittstelle

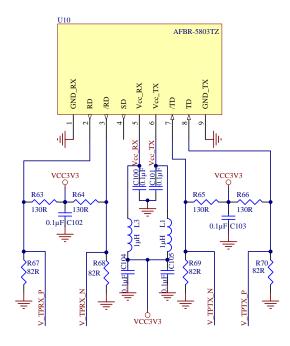

Die elektrische Schnittstelle zum Transceiver wird durch zwei Leitungspaare für DATA-Receive (RD+/RD-) und DATA-Transmit (TD+/TD-) realisiert. Für die schnelle Datenübertragung mit 125 Mbit/s wird die bereits erwähnte schnelle PECL-Logik eingesetzt. Allerdings benötigt die PECL-Logik zusätzliche Arbeitswiderstände (R63 bis R70), die auch als Terminierung dienen. Die Abbildung 3.36 zeigt die Verdrahtung des optischen Transceivers.

Die Besonderheit des AFBR-5803ATZ Transceivers im Vergleich zu anderen Typen wie AFBR-5103 liegt in der 3,3 V kompatiblen Versorgungsspannung. Bei einem Betrieb mit 5 V Versorgungsspannung wäre eine zusätzliche Pegelanpassung zum Realtek Chip nötig, der mit 3,3 V Versorgungsspannung arbeitet. Weil die Pegel bei PECL von der Versorgungsspannung de-

Abbildung 3.36: Elektrische Schnittstelle zum AFBR-5803

finiert werden und sich bei unterschiedlichen Versorgungsspannungen verschieben würden, kommt eigentlich nur eine 3,3 V Variante in Frage. Zusätzlich wurde festgestellt, dass die Erwärmung des Transceivers und damit die Verlustleistung bei 3,3 V Versorgungsspannung deutlich geringer ist. Eine minimale Verlustleistung ist besonders wichtig, weil das Gehäuse nahezu luftdicht abgeschlossen ist und keine Luftzirkulation zulässt. Die elektrische Schnittstelle für den 100Base-TX Standard ist im Schaltplan zu finden (siehe Anhang A.2).

#### 3.7.2.7 Optische Schnittstelle

Für den Anschluss des Lichwellenleiters werden ST-Steckverbindungen verwendet, die eine geringe Einfügungsdämpfung von ca. 0.3 dB haben und für passive Patchfelder geeignet sind (Abbildung 3.37). Der ST-Stecker ist besonders robust und bietet einen Bayonett-Verschluss gegen Selbstlösung.

Die Stecker entsprechen dem vorhandenen System in Effelsberg und können ohne Übergangselemente verwendet werden. Die passenden Kupplungen und Patchkabel ermöglichen eine einfache Trennung vom Gerät und eine individuelle Platzierung des Transceivers. Durch die metallische Ausführung der Kupplung und Stecker werden die Austrittsöffnungen nahezu komplett abgeschirmt und verhindern das Austreten von elektromagnetischen Wellen. Die Abbildung 3.38 zeigt die

Abbildung 3.37: St-Stecker und Kupplung (Foto: Huber+Suhner)

realisierte Ethernet-Schnittstelle und Entkopplung nach außen. Bei der Verlegung des Lichtwellenleiters sollte man darauf achten, dass der vom Hersteller vorgegebene Biegeradius nicht unterschritten wird.

Abbildung 3.38: Trennung durch eine LWL Kupplung

## 3.7.2.8 Test der optischen Übertragungsstrecke

Vor Einbindung der neu entwickelten Ethernet-Schaltung in das Gesamtsystem wurde die Schaltung auf Funktion geprüft. Da es noch keine Erfahrungen in der Entwicklung von optischen Ethernet-Schnittstellen am Institut gab und um sich zu vergewissern, dass die Datenübertragung auch über mehrere hundert Meter einwandfrei funktioniert, wurde ein kleines Testsystem aufgebaut und im Teleskop Effelsberg erprobt. Dazu wurde eine ca. 700 Meter lange Teststrecke mit mehreren Patchstellen aufgebaut. Damit entsprach die Teststrecke der doppelten Länge der tatsächlichen Übertragungsstrecke. Mit dem Versuch sollte garantiert werden, dass das System bei einer 300 bis 350 Meter langen Übertragungsstrecke einwand-

frei funktioniert. Durch mehrere Patchstellen konnte die Einfügungsdämpfung in das System einbezogen werden. Die für den Test benötigte Software bestand aus einem kleinen Programm im FPGA für die Testdatengenerierung und einem »LABVIEW-Programm « für den Datenempfang über TCP/IP. Zum Debuggen wurde das Programm »WireShark « verwendet.

Die Datenübertragung verlief tadellos und erreichte mit ca. 25 Mbit/s sogar eine etwas höhere Datenrate als vom Hersteller spezifiziert. Damit sollte die entwickelte Schaltung auch unter realen Bedingungen funktionieren.

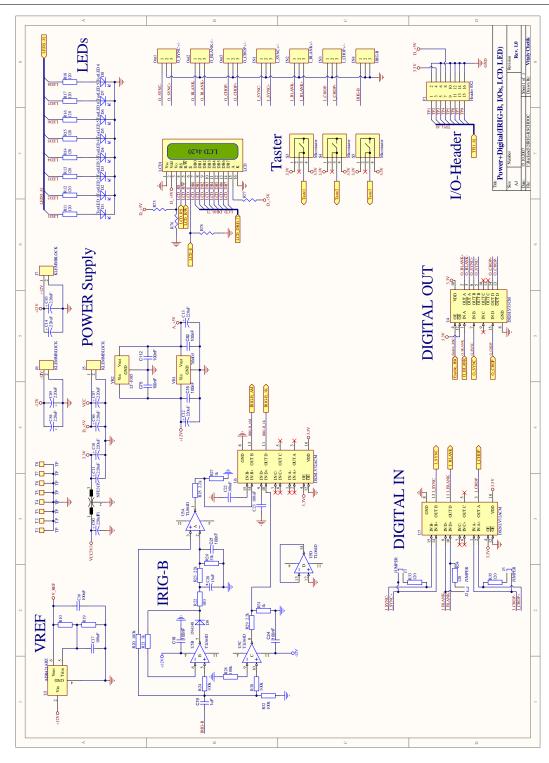

## 3.7.3 Digitale Steuersignale

### 3.7.3.1 Digitale Eingänge

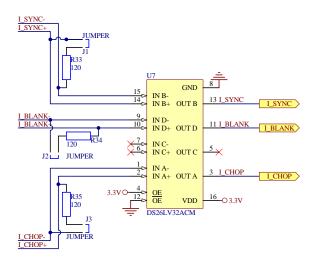

Um sich auf die Messphasen einsynchronisieren zu können, werden in Effelsberg zwei Steuersignale (BLANK und SYNC) zur Verfügung gestellt. Die beiden BLANK- und SYNC-Signale liegen als differentielle RS-422-Signal vor. Damit sind sie unempfindlich gegen Gleichtaktstörung und ermöglichen eine Datenübertragung über mehrere hundert Meter. Um eine externe CHOP-Frequenz vorgeben zu können, wurde das Backend um ein zusätzliches Eingangssignal erweitert. Um die Kompatibilität zum bestehenden System zu erhalten, wurde es ebenfalls als differentielles Eingangssignal realisiert. Für die Pegelwandlung auf LVTTL

Abbildung 3.39: Differentielle Eingänge für Steuersignale

wurde ein »Differential Line Receiver« DS26LV32 verwendet. Mit seinen vier differentiellen Eingängen deckt er den gesamten Bedarf ab. Die Termininierung der Leitungen kann auf Wunsch über Jumper gesetzt werden. Die Abbildung 3.39 zeigt die realisierte Schaltung.

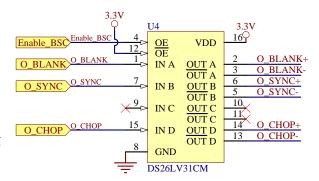

### 3.7.3.2 Digitale Ausgänge

Als Ausgangssignal wird hauptsächlich die CHOP-Frequenz benötigt. Um auch unabhängige Messungen machen zu können, ermöglicht das neue Backend eigene Generierung von BLANK- und SYNC-Signalen. Um ebenfalls kompatibel zum bestehenden System zu bleiben, wurde für die Pegelwandlung von LVTTL auf RS-422 ein » Differential Line Driver « DS26LV31 verwendet. Die Abbildung 3.40 zeigt die realisierte Schaltung.

Abbildung 3.40: Differentielle Ausgänge für Steuersignale

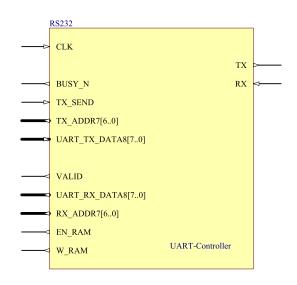

### 3.7.4 RS-232 Schnittstelle

Während der Entwicklungsphase ist die Anzeige oder Veränderung von bestimmten Zuständen und Signalen besonders wichtig. Da kann eine RS-232-Schnittstelle oft von Vorteil sein und gibt einem die Möglichkeit, z.B. über ein Terminal mit dem System zu kommunizieren. Zusätzlich ermöglicht sie eine direkte ASCII-Zeichen Übertragung an das Display oder EE-PROM. Für die Pegelanpassung von TTL auf RS-232 wurde ein MAX232 eingesetzt. Weil man in der Endversion auf die RS-232-Schnittstelle verzichten kann, wurde die Schaltung auf einer einfachen Lochrasterplatine aufgebaut und über freie I/Os des FPGAs angebunden. Aufgrund der einfachen Schaltung wird auf eine ausführliche Beschreibung an dieser Stelle verzichtet. Nähere Informationen zum MAX232 können dem Datenblatt im Anhang B entnommen werden.

### 3.7.5 Bedienelemente

Um eine komfortable Bedienung des Gerätes zu ermöglichen, wurde es mit einem einfachen Zeichendisplay und einigen Tastern ausgestattet. Damit lässt sich z.B. die IP-, MAC-, SUB-Adresse oder die Schaltfrequenz anzeigen und verändern. Auch während der Entwicklungsphase waren die Taster und das Display sehr hilfreich.

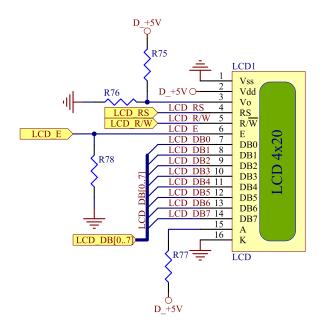

## 3.7.5.1 LCD - Displaytech Ltd 204A Series

Das LCD hat einen integrierten ASCII-Zeichengenerator und Interface-Controller. Die Ansteuerung erfolgt über eine einfache 4/8 Bit Parallelbus-Schnittstelle, die im Abschnitt 6.4 auf Seite 60 näher beschrieben wird. Die Abbildung 3.41 zeigt die realisierte Verschaltung des Displays. Mit Hilfe der beiden Widerstände R75 und R76 am Vo-Anschluss kann der Kontrast angepasst werden. Der Pullup-Widerstand R78 am Enable-Pin sorgt für einen LOW-Pegel beim Einschalten des Gerätes, sonst kann es zur Fehlkonfiguration des Displays kommen.

Abbildung 3.41: Zeichendisplay

## 3.7.6 I<sup>2</sup>C-EEPROM - Atmel AT24C512

Weil das eingesetzte FPGA nur einen flüchtigen Speicher hat und alle Einstellungen nach dem Abschalten der Versorgungsspannung verliert, können keine Änderungen von z.B. IP-Adresse oder anderen Parametern dauerhaft gespeichert werden. Zur Abhilfe wird ein 512 kBit großes EEPROM verwendet, das ausreichend Platz für alle Einstellungen bietet.

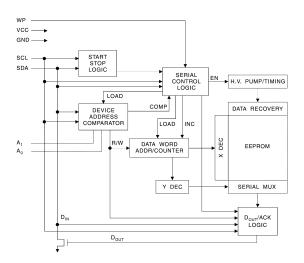

Der eingesetzte EEPROM wird über eine l<sup>2</sup>C-Schnittstelle angesprochen und kommt mit nur zwei Signalleitungen, SDA und SCL, aus (Abbildung 3.42). Auf externe Pullup-Widerstände für die Open-Collector-Ausgänge wurde verzichtet, weil diese im

Abbildung 3.42: Blockschaltbild des AT24C512 (Atmel)

FPGA zugeschaltet werden können. Möchte man mehrere Teilnehmer am I<sup>2</sup>C-Bus ermöglichen, können mit Hilfe von A0 und A1 unterschiedliche Adresse vergeben werden. Am WP-Anschluss kann das EEPROM in den Schreibschutz-Modus versetzt werden.

Die Übertragungsrate hängt von der Versorgungsspannung ab und muss bei der Programmierung berücksichtigt werden. Um kompatibel zum FPGA zu sein, muss mit 3,3 V gearbeitet werden. Damit sollte sich eine Baudrate von bis zu 500 kBaud/s realisieren lassen (1 MBaud/s @ 5 V, 400 kBaud/s @ 2.7 V und 100 kBaud/s @ 1.8 V). Aufgrund einiger freien I/Os am FPGA wurden alle Signale verdrahtet. Damit ermöglicht man einen Einsatz von anderen EEPROM-Typen. Nähere Informationen zum AT24C512 können dem Datenblatt entnommen werden. Die Kommunikation mit dem I<sup>2</sup>C EEPROM wird im Abschnitt 6.3 auf Seite 58 näher beschrieben.

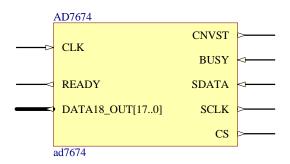

### 3.7.7 Schnittstelle zum AD-Wandler AD7674

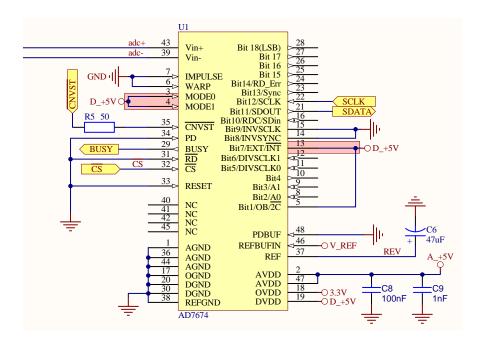

Der hier beschriebene Schaltungsteil bezieht sich nur auf die digitale Seite des AD-Wandlers. Der Analogteil wurde bereits in Abschnitt 3.1.1 auf Seite 9 beschrieben.

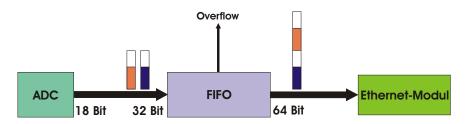

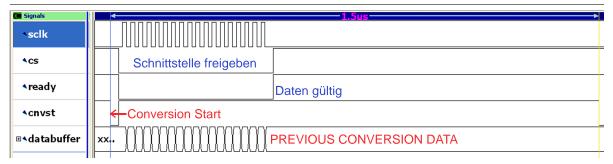

Das Auslesen des AD7674 kann sowohl über eine parallele als auch über eine serielle Schnittstelle erfolgen. Aufgrund der hohen Anzahl an Wandlern und begrenzter Anzahl an FPGA-I/Os kann keine unabhängige Ansteuerung eines jeden AD-Wandlers realisiert werden. Bei Parallelschaltung kann die Auslesung nur im Multiplexverfahren erfolgen. Mit steigender Anzahl und Abtastrate der AD-Wandler wird die parallele Schnittstelle zum Flaschenhals. Dagegen bietet die serielle Schnittstelle eine von Anzahl und Abtastrate unabhängige Auslesegeschwindigkeit. Die Konfiguration für den »SLAVE SERIAL MODE« ist im Schaltplan in Abbildung 3.43 auf der nächsten Seite durch rote Felder gekennzeichnet. Das Auslesen der Daten wird in Abschnitt 6.2 auf Seite 57 näher beschrieben.

Abbildung 3.43: Verdrahtung des AD7674

### 3.7.8 IRIG-B AM-Demodulator

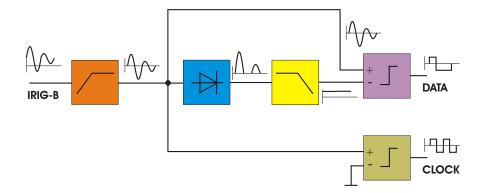

Für eine genaue Zeiterfassung während den Messphasen existiert im Teleskop Effelsberg ein GPS-basiertes Zeitsignal, das im IRIG-B-Format übertragen wird. Für die Demodulation des IRIG-B-Signals wird ein AM-Demodulator benötigt. Der AM-Demodulator ist eine bereits bestehende Schaltung aus dem Digitallabor, die lediglich auf geeignete Versorgungsspannungen untersucht und in die eigene Schaltung eingebunden wurde. Deshalb wird hier auf eine ausführliche Beschreibung verzichtet. Der gesamte Schaltplan und VHDL-Code des Autors ist im Anhang A und E zu finden. Mit Hilfe des Blockschaltbildes in Abbildung 3.44 auf der nächsten Seite soll die Funktionsweise kurz erläutert werden.

Abbildung 3.44: AM-Demodulator

- 1. Das IRIG-B Signal kommt mit einer digital modulierten Amplitude und einem Träger am Eingang des Demodulators an.

- 2. Der vorgeschaltete Hochpass sorgt für eine Gleichspannungsunterdrückung des Eingangssignals.

- 3. Im mittleren Zweig sorgt eine Diode für das Gleichrichten des Signals. Dadurch entsteht am Ausgang eine Gleichspannung mit überlagerter Wechselspannung.

- 4. Der nachgeschaltete Tiefpass sorgt für die Unterdrückung aller Wechselspannungsanteile.

- 5. Der gewonnene Mittelwert wird mit dem Eingangssignal am Komparator verglichen und zu einem digitalen Signal umgeformt.

- 6. Im unteren Zweig wird mit Hilfe eines weiteren Komparators das Eingangssignal zu einem digitalen Signal umgeformt und als Taktsignal verwendet.

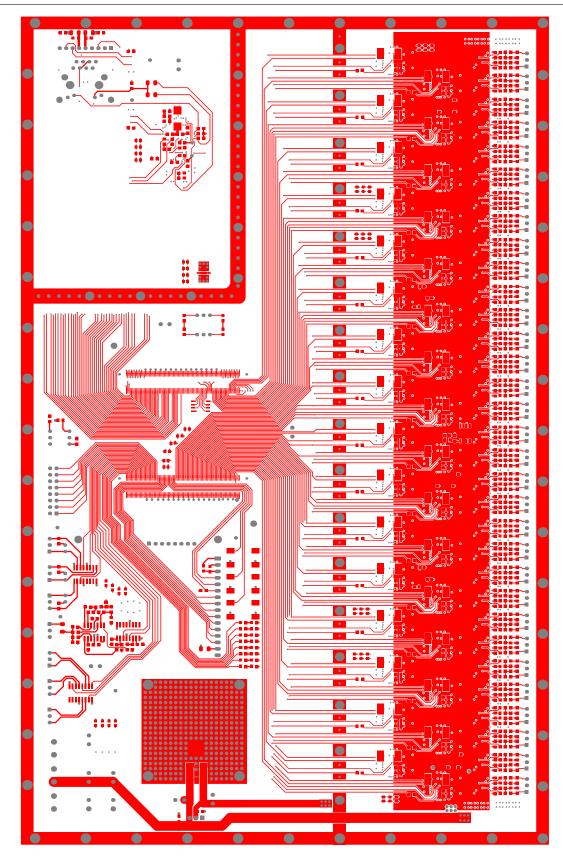

# 4 Layout

Aufgrund der hohen Ansprüche an das Backend muss auch das Layout sehr sorgfältig durchdacht sein. Besonders wichtig ist die örtliche Trennung, Singalintegrität und Entkopplung der einzelnen Baugruppen. Das gesamte Layout ist im Anhang C zu finden.

# 4.1 Örtliche Trennung

Die örtliche Trennung ist besonders für gemischte Schaltungen von großer Bedeutung. Es muss darauf geachtet werden, dass die empfindliche analoge Elektronik sich in einem möglichst großen Abstand von der digitalen Elektronik befindet. Bei einem nicht ausreichenden Abstand machen sich Effekte wie Übersprechen durch elektrische und magnetische Felder oder Kopplung durch gemeinsame Impedanz sehr schnell bemerkbar. Die Abbildung 4.1 zeigt die notwendige Trennung der einzelnen Baugruppen. An den gold markierten Flächen am Rand und um die einzelnen Schaltungen herum soll später das Gehäuse mit einer möglichst geringen Impedanz angebunden werden können. Durch Trennung in einzelne Kammern wird eine noch höhere Entkopplung über den freien Raum erreicht.

Abbildung 4.1: Örtliche Trennung der Baugruppen

# 4.2 Lagenaufbau

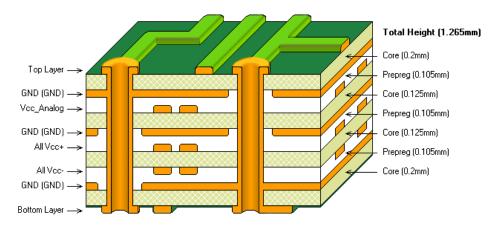

Der Lagenaufbau ist hauptsächlich von den notwendigen Versorgungsspannungen und Signalleitungen abhängig und wurde wie folgt festgelegt (Abbildung 4.2):

Abbildung 4.2: Lagenaufbau

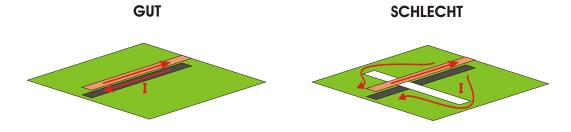

Die beiden äußeren Lagen, Top und Bottom, wurden für Signalleitungen verwendet, der Top-Layer hauptsächlich für digitale und der Bottom-Layer für analoge Signale. Um eine maximale Abschirmung und Singalintegrität zu gewährleisten, wurde unter jeder Signallage eine komplette GND-Lage verlegt. Damit schafft man einen ungestörten Hin- und Rückfluss des elektrischen Stromes und verhindert eine Abstrahlung an Diskontinuitäten bei hohen Frequenzen. Die Abbildung 4.3 zeigt den Unterschied zwischen einem gestörten und ungestörten Stromfluss.

Abbildung 4.3: Hin- und rückfließender Strom in Leiterbahnen

Damit es auch keine kapazitive Kopplung zwischen der analogen Versorgungsspannung für die AD-Wandler und den digitalen Versorgungsspannungen gibt, wurde eine zusätzliche GND-Lage als Trennung verwendet.

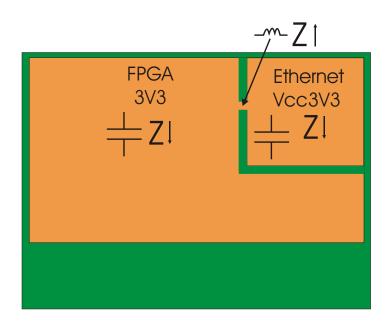

# 4.3 Entkopplung der Versorgungsspannungen

Besonders wichtig ist die Entkopplung zwischen den analogen und digitalen Versorgungsspannungen. Eine effektive Entkopplung erreicht man durch Bilden von Inseln. Im unteren Frequenzbereich verhindert man damit eine gemeinsam durchflossene Impedanz, weil der Stromfluss auf die Insel begrenzt wird und bei hohen Frequenzen entsteht durch die Geometrie der Lagen ein Tiefpass zwischen den beiden Versorgungsspannungen. Die Abbildung 4.4 zeigt die Entkopplung der Ethernet-Versorgungsspannung auf eine solche Art und Weise. Das Gleiche gilt auch für alle anderen Versorgungsspannungen.

Abbildung 4.4: Entkopplung der Versorgungsspannungen

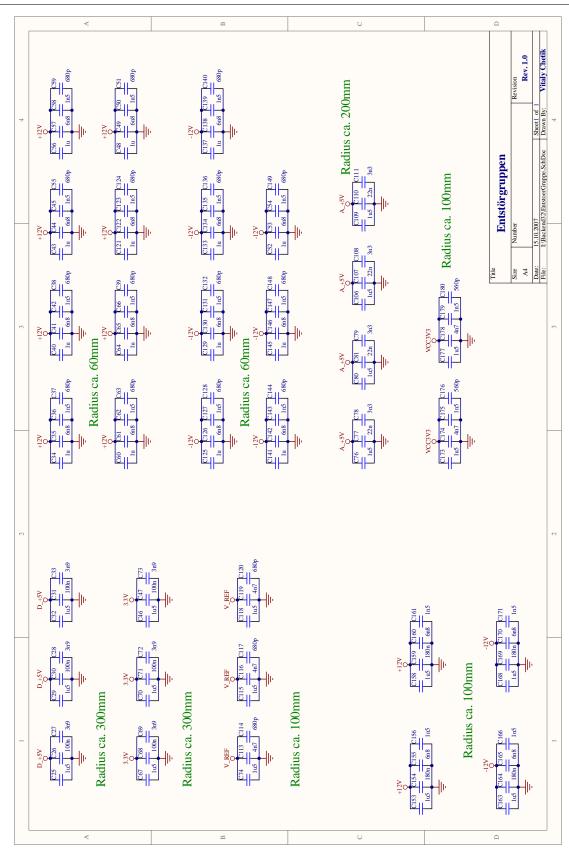

# 4.4 Entstörung und Stabilisierung der Versorgungsspannung

Die Entstörung und Stabilisierung der Versorgungsspannungen wurde nach der neusten Methode der Technik durchgeführt. Dabei ersetzt man zum einen die Puffer-Kondensatoren durch ganze Gruppen an Kondensatoren und zum anderen nutzt man die Kapazität zwischen den einzelnen Versorgungslagen aus. Diese Methode ist erst seit der Herstellung von Multi-Layer Platinen mit einem Lagenabstand von ca. 100  $\mu$ m möglich geworden.

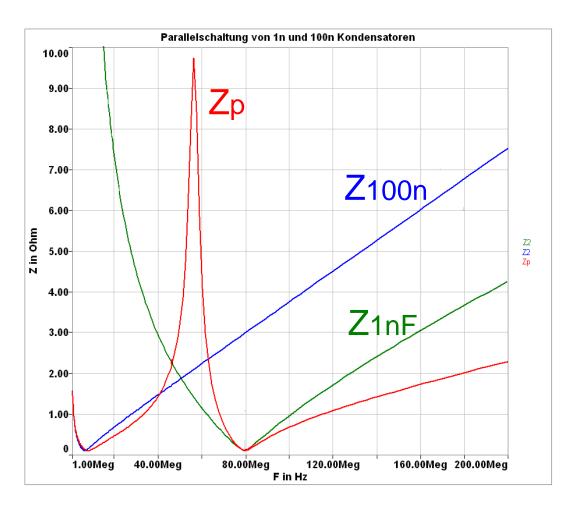

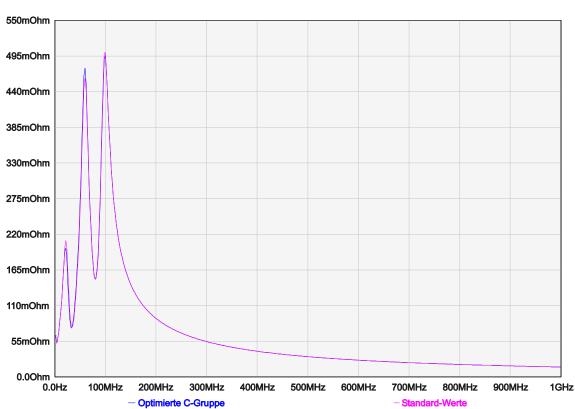

Für die Stabilisierung der Versorgungsspannung im unteren Frequenzbereich, bis etwa 10 kHz, werden immer noch Elektrolyt- oder Tantalkondensatoren verwendet. Für höhere Frequenzen lässt ihre Wirkung stark nach und fordert den Einsatz von Keramikkondensatoren. Aber auch diese haben je nach Kapazitätswert nur bis zu einer bestimmten Frequenz ein kapazitives Verhalten und müssen durch Parallelschaltung von ganzen Gruppen aus unterschiedlichen Werten zusammengesetzt werden. Allerdings führt eine beliebige Parallelschaltung zu dem Problem, dass aus der Induktivität des einen und der Kapazität des anderen Kondensators ein Parallelschwingkreis entsteht, der in einem bestimmten Frequenzbereich die Impedanz anhebt und eine Entstörung nicht mehr möglich macht. Die Abbildung 4.5 zeigt den Impedanzverlauf einer Parallelschaltung aus zwei Kondensatoren mit 1 und 100 nF. Es ist auch zu erkennen, dass selbst ein SMD Kondensator mit 1 nF ab einer Frequenz von 80 MHz ein rein induktives Verhalten hat und eine effektive Entstörung unmöglich macht.

Abbildung 4.5: Problem der Parallelschaltung von Kondensatoren

Mit Hilfe einer speziellen Software »Silent« kann die Parallelschaltung von Kondensatoren berechnet werden. Auch die Geometrie der Versorgungslagen wird in die Berechnung einbezogen und auf Entstörwirkung untersucht. Durch Vorgabe der gewünschten Impedanz und Baugröße der Kondensatoren liefert die Software eine passende Entstörgruppe. Die Abbildung 4.6 zeigt den Impedanzverlauf der 3,3 V Versorgungsspannung. Durch die große Fläche und den geringen Lagenabstand lässt sich die Wirkung der Lagenkapazität bereits ab 100 MHz erkennen.

SILENT für Windows V. 3.0 Copyright 1992-2003 by Dirks Corporate Consulting

Abbildung 4.6: Optimierte Entstörgruppen

# 5 Gehäuseentwurf

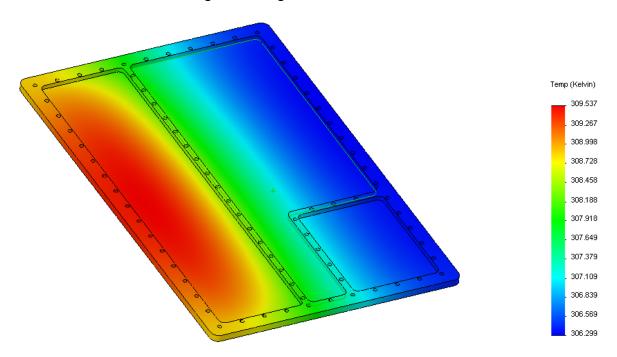

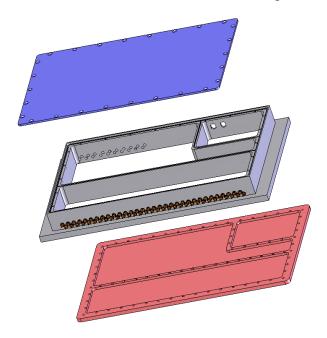

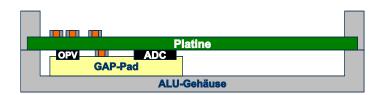

Weil das Backend in unmittelbarer Nähe des Empfängers montiert werden soll und hauptsächlich aus digitaler Elektronik besteht, muss für eine ausreichende Abschirmung gesorgt werden. Eine gute Abschirmung hat ein luftdichtes Gehäuse zu Folge und verhindert damit eine ausreichende Luftzirkulation. Um Hitzestau zu vermeiden, muss die entstandene Verlustleistung über das Gehäuse abgeführt werden. Außerdem soll das Gehäuse in ein 19-Zoll-Rack mit 3HE passen.

# 5.1 Abschirmung

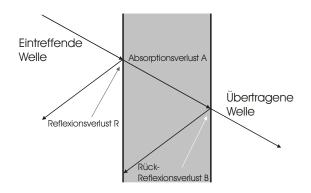

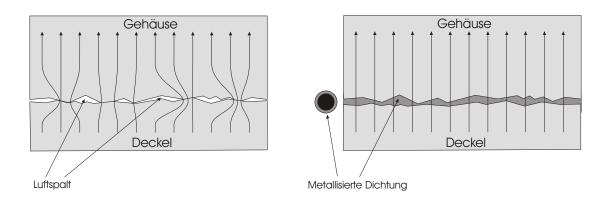

Die Abschirmung beruht auf dem Prinzip der Reflexion und Absorption. Trifft eine elektromagnetische Welle auf eine ebene Metalloberfläche, so entstehen dort Ströme und Ladungsverschiebungen. Bei einer geringen Oberflächenimpedanz entsteht hauptsächlich eine im Gegensinn erzeugte Welle. Die teilweise eingedrungenen Ströme werden durch das Material absorbiert. Sind die Verluste im Material nicht ausreichend hoch genug so kann es zu Durchdringung des Materials führen und zum neuen Wechselfeld (Abbildung 5.1).

Abbildung 5.1: Reflexion und Absorption einer elektromagnetischen Welle

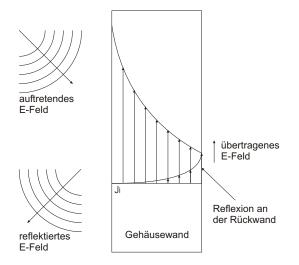

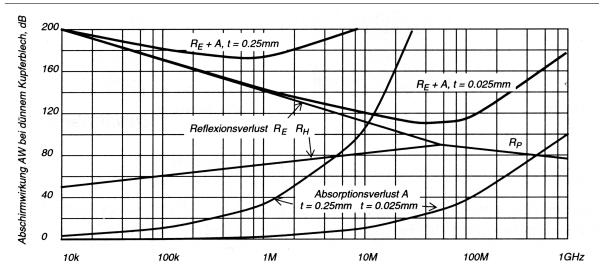

### 5.1.1 Reflexionsverluste

Der Reflexionsverlustfaktor R wird durch das Verhältnis Wellenimpedanz zu Wandimpedanz bestimmt. Besonders gut leitfähige Materialien wie Silber, Kupfer, Gold und Aluminium haben einen hohen E-Feld Reflexionsverlustfaktor. Allerdings würden Silber und Gold aus Kostengründen nicht in Frage kommen. Die Wandimpedanz ist eine Funktion aus Leitfähigkeit, Permeabilität und der Frequenz. Bei der Wellenimpedanz muss eine Fallunterscheidung gemacht werden. In einem ausreichenden Abstand, größer  $\lambda/2 \cdot \pi$ , kann man von einer ebenen Welle mit einem Wellenwiderstand von 377  $\Omega$  sprechen. Im Nahfeld muss das elektrische und magnetische Feld einzelnen Betrachtungen unterzogen werden. Mit nachfolgenden Gleichungen 5.1 bis 5.3 [Williams 2000, S. 292] kann eine gute Abschätzung über die Reflexionsverluste gemacht werden.

Ebene Welle:

$$\frac{R}{dB} = 168 - 10 \cdot log((\frac{\mu_r}{\sigma_r}) \cdot f) \tag{5.1}$$

Elektrisches Feld:

$$\frac{R_E}{\mathsf{dB}} = 322 - 10 \cdot \log((\frac{\mu_r}{\sigma_r}) \cdot f^3 \cdot r^2) \tag{5.2}$$

Magnetisches Feld:

$$\frac{R_H}{dB} = 14, 6 - 10 \cdot log((\frac{\mu_r}{\sigma_r}) \cdot f \cdot r^2)$$

(5.3)

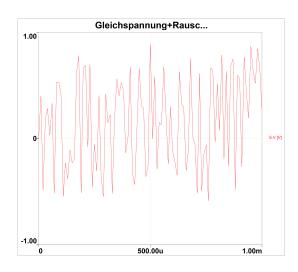

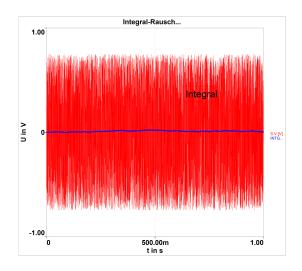

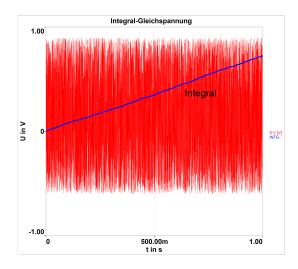

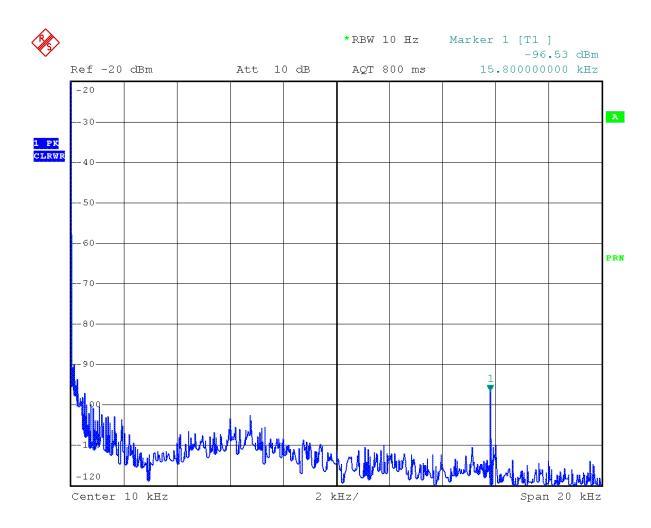

## 5.1.2 Absorptionsverluste